This is the peer reviewd version of the followng article:

Mechanisms of Step-Stress Degradation In Carbon-Doped 0.15 μm AlGaN/GaN HEMTs for Power RF Applications / Zagni, Nicolo'; Zhan, Veronica Gao; Verzellesi, Giovanni; Chini, Alessandro; Pantellini, Alessio; Natali, Marco; Lucibello, Andrea; Latessa, Luca; Lanzieri, Claudio; Santi, Carlo De; Meneghini, Matteo; Meneghesso, Gaudenzio; Zanoni, Enrico. - In: IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY. - ISSN 1530-4388. - 23:(2023), pp. 453-460. [10.1109/TDMR.2023.3305033]

Terms of use:

The terms and conditions for the reuse of this version of the manuscript are specified in the publishing policy. For all terms of use and more information see the publisher's website.

22/05/2024 05:26

# Mechanisms of step-stress degradation in Carbon-doped 0.15 µm AlGaN/GaN HEMTs for power RF applications

Nicolò Zagni, *Member, IEEE*, Veronica Zhan Gao, Giovanni Verzellesi, *Senior Member, IEEE*, Alessandro Chini, Alessio Pantellini, Marco Natali, Andrea Lucibello, Luca Latessa, Claudio Lanzieri, Carlo De Santi, *Member, IEEE*, Matteo Meneghini, *Senior Member, IEEE*, Gaudenzio Meneghesso, *Fellow, IEEE*, and Enrico Zanoni, *Life Fellow, IEEE*

Abstract-We discuss the degradation mechanisms of Cdoped 0.15-µm gate AlGaN/GaN HEMTs tested by drain step-stress experiments. Experimental results show that these devices exhibit cumulative degradation effects during the step stress experiments in terms of either (i) transconductance (gm) decrease without any thresholdvoltage ( $V_T$ ) change under OFF-state stress, or (*ii*) both  $V_T$ and gm decrease under ON-state stress conditions. To aid the interpretation of the experiments, two-dimensional hydrodynamic device simulations were carried out. Based on obtained results, we attribute the g<sub>m</sub> decrease accumulating under OFF-state stress to hole emission from C<sub>N</sub> acceptor traps in the gate-drain access region of the buffer, resulting in an increase in the drain access resistance. On the other hand, under ON-state stress, channel hot electrons are suggested to be injected into the buffer under the gate and in the gate-drain region where they can be captured by  $C_N$  traps, leading to  $V_T$  and  $g_m$ degradation, respectively.

*Index Terms*—GaN HEMTs, Step Stress, Carbon Doping, Hot Electrons, Reliability.

# I. INTRODUCTION

GALLIUM Nitride (GaN)-based high electron mobility transistors (HEMTs) are considered to be a key enabling technology for high frequency communication systems [1], [2]. High mobility and breakdown voltage of GaN-based devices are fundamental physical properties that allow realizing highly efficient power amplifiers [3], [4]. Short channel length (i.e.,

N. Zagni and A. Chini are with the Department of Engineering "Enzo Ferrari", University of Modena and Reggio Emilia, 41125, Modena, Italy. (N. Zagni and V. Z. Gao contributed equally to this work.) (e-mail: <u>nicolo.zagni@unimore.it</u>).

V. Z. Gao, C. De Santi, M. Meneghini, G. Meneghesso, and E. Zanoni are with the Department of Information Engineering (DEI), University of Padova, 35131, Padova, Italy.

G. Verzellesi is with Department of Sciences and Methods for Engineering (DISMI), University of Modena and Reggio Emilia, 42122, Reggio Emilia, Italy and EN&TECH Center, University of Modena and Reggio Emilia, 42122, Reggio Emilia, Italy.

A. Pantellini, M. Natali, A. Lucibello, L. Latessa and C. Lanzieri are with Leonardo Company, Via Tiburtina km 12,400, 00131, Rome, Italy.

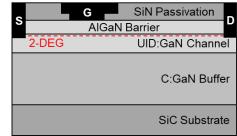

Fig. 1. Sketch of the 0.15  $\mu m$  AlGaN/GaN C-doped HEMT under study in this work.

<1µm) GaN HEMTs are pursued to achieve the high  $f_T$  and  $f_{max}$  required for microwave operation. However, shortening the gate length affects the electrostatic integrity of the device due to undesirable short-channel effects (SCEs) with detrimental effect on the linear power gain. Moreover, a large breakdown voltage is required to increase the RF output power. To keep SCEs under control and to increase the breakdown voltage, foreign impurities are introduced in the GaN buffer underneath the channel layer so as to pin the Fermi-level well below the conduction band edge, hence reducing buffer conductivity [5], [6].

The most widely employed impurity species in GaN RF HEMTs is iron (Fe) [6], while carbon (C) is more generally used in power devices for switching converters [7]. However, due to similarity of HEMT epitaxial layers growth conditions for both RF and power applications, C can also be incorporated as background impurity in nominally Fe-doped only buffer [8]. C is also being investigated as an alternative to Fe as buffer doping species (i.e., it is intentionally incorporated) for RF applications as well [9]. Despite GaN HEMTs complying with stability/reliability requirements of commercial applications have already been demonstrated, a deeper assessment of the related limiting mechanisms is required for the further development of the technology [10].

In this work, we present results from OFF- and ON-state drain step-stress tests on 0.15-µm gate C-doped AlGaN/GaN HEMTs, extending a recent conference paper of ours [9] by providing a more complete assessment of the proposed physical degradation mechanisms. Distinctive degradation modes are in

Copyright © 2023 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained by sending a request to <u>pubs-permissions@ieee.org</u>

fact pointed out by our measurements for OFF-state and ONstate stresses and attributed, also with the aid of simulation results, to the different charging mechanisms of C-related acceptor traps in the C-doped buffer for the two stress conditions.

Specifically, OFF-state degradation is shown to be characterized by a transconductance  $(g_m)$  decrease, especially in the high-current regime, which is attributed to hole emission from C-related acceptors and the consequent increase in the drain access resistance. ON-state stress instead results in threshold-voltage ( $V_T$ ) increase as well as  $g_m$  decrease (both peak and high-current values), which can be explained by the injection of channel hot electrons (CHEs) into the buffer and to the surface, and consequent electron trapping into C-related acceptors and surface traps, respectively.

Since dominant C-related traps are  $C_N$  levels at 0.9 eV from the GaN valence band, i.e., at 2.5 eV from the conduction band, they "naturally" behave as hole traps, by emitting holes when the depletion region in the weakly p-type buffer widens in response to the negative gate-drain voltage applied under the OFF-state stress conditions. If emitted holes do not exit from the device or recombine with electrons, they can be re-trapped by  $C_N$  levels as the OFF-state stress bias is removed, leading to a long-time-constant drain current (and transconductance) recovery, which does not necessarily finish before the application of the subsequent stress step.

On the other hand, ON-state stress completely perturbs this quasi-equilibrium picture because of the injection of channel electrons into the buffer. Part of these electrons can be trapped by neutral  $C_N$  levels. The attending electron-hole recombination inside the traps leads to a virtually permanent negative charge buildup, owing to the 2.5 eV offset from the conduction band, that can only be recovered by high temperature or suitable illumination.

The paper is organized as follows. In Section II, a description of the tested devices and of the step-stress measurement setup is provided. In Section III, we present the results of the stress characterizations. In Section IV, we provide the simulation results supporting the interpretation of the observed experimental behavior. Section V draws the conclusions of this work.

### II. DEVICES AND EXPERIMENTAL SETUP

Devices under test (DUTs) are Schottky-gate AlGaN/GaN HEMTs with 0.15- $\mu$ m gate length ( $L_G$ ) and 4- $\mu$ m long drain-tosource spacing ( $L_{SD}$ ), fabricated onto SiC wafers and featuring a C-doped GaN buffer layer for achieving a high voltagehandling capability and a 100-nm undoped GaN channel to minimize current-collapse effects [9]. DUTs were fabricated by Leonardo on commercial wafers. Key performance parameters are as follows:  $f_T = 20.4$  GHz,  $f_{max} = 43$  GHz, maximum power gain  $G_{max}=19$  dB (at 5.5 GHz), output power  $P_{out}= 7$  W/mm (at 5.5 GHz), drain efficiency DE = 70% (at 5.5 GHz). Figure 1 shows a sketch of the device cross-section.

DC drain-current ( $I_D$ ) vs gate-source-voltage ( $V_{GS}$ ) curves were acquired at constant drain-source voltage ( $V_{DS}$ ) prior to applying the step-stress sequence, representing the curve labeled ( $V_{GS,STR}$ ,  $V_{DS,STR}$ ) = (0, 0) V in the plots. DUTs were submitted to both OFF-state and ON-state step-stress tests by

2

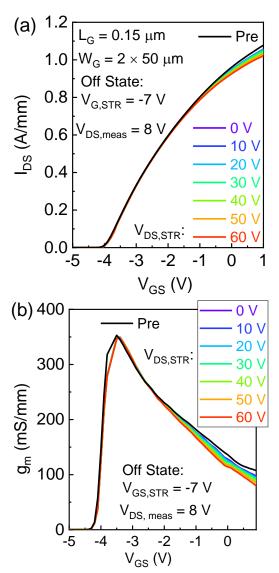

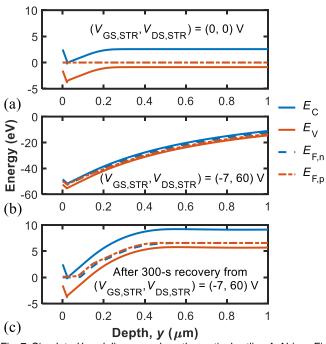

Fig. 2. (a) Drain-current ( $I_D$ ) and (b) transconductance ( $g_m$ ) vs gatesource-voltage ( $V_{GS}$ ) curves measured after each step of the drain stepstress experiment carried out on the DUTs under OFF-state conditions.

applying either  $V_{\text{GS,STR}} = -7$  V or  $V_{\text{GS}} = 0$  V, respectively.  $V_{\text{DS,STR}}$  was ramped from 0 V to 60 V in both conditions with 5-V steps. Each stress step was maintained for 120 s followed by a 300-s unbiased step after which a complete DC  $I_{\text{D}}$ - $V_{\text{GS}}$  is acquired.

#### **III. STRESS EXPERIMENTS**

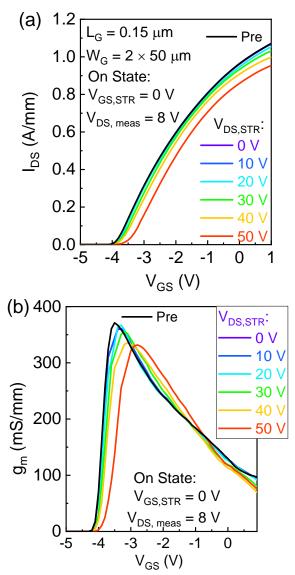

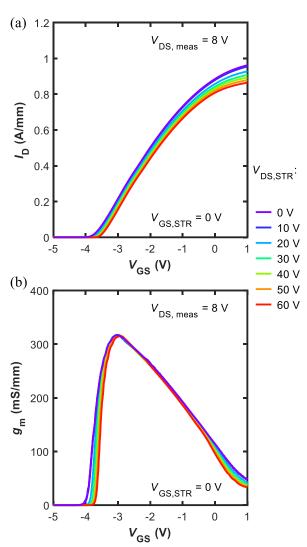

Key experimental results are shown in Figs. 2 and 3, reporting the  $I_{\rm D}$ - $V_{\rm GS}$  and  $g_{\rm m}$ - $V_{\rm GS}$  curves measured after each stress step under either OFF-state, see Fig. 2, or ON-state conditions, see Fig. 3.

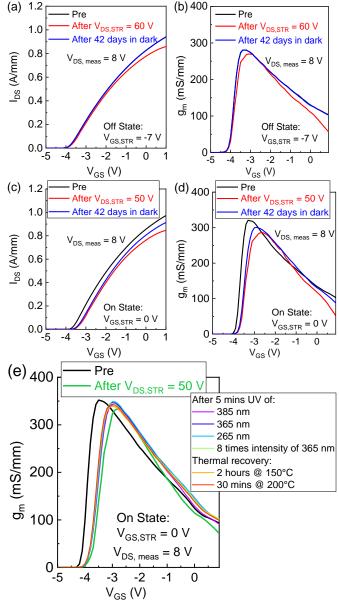

The OFF-state stress resulted, after the final step at ( $V_{GS,STR}$ ,  $V_{DS,STR}$ ) = (-7, 60) V in a small  $g_{m,max}$  (at  $V_{DS} = 8$  V) drop of 1.2%, see Fig. 2(b), while  $V_T$  (the  $V_{GS}$  when  $I_{DS} = 1$  mA/mm at  $V_{DS} = 8$  V) showed no appreciable drift, see Fig. 2(a). Conversely, the ON-state stress induced after the ( $V_{GS,STR}$ ,  $V_{DS,STR}$ ) = (0, 60) V step a 9.6%  $g_m$  decrease, see Fig. 3(a), accompanied by a 0.32 V  $V_T$  increase, see Fig. 3(b). Devices

Fig. 3. (a) Drain-current ( $I_D$ ) and (b) transconductance ( $g_m$ ) vs gatesource-voltage ( $V_{GS}$ ) curves measured after each step of the drain stepstress experiment carried out on the DUTs under ON-state conditions.

fabricated with the same processing onto wafers with Fe-doped buffer and subjected to same step-stress experiments exhibit much smaller degradation effects for both OFF- and ON-state stress conditions, indicating that degradation effects observed in the step-stress experiments are related to C-doping in the buffer [9].

OFF-state degradation can be explained as follows. Prolonged bias in the OFF-state is well-known to trigger dispersion effects related to C-doping [7], [11]–[13], which can be explained by the 'hole-redistribution' model as long as the source-drain punch-through current remains negligible [14]. According to the latter, during the OFF-state stress, holes are predominantly emitted from  $C_N$  states within the gate-drain depleted region of the buffer, move to the gate-source and the bottom regions of the buffer and get captured by the same  $C_N$  states therein, so that they need to be re-emitted from the latter traps, move back and then be re-captured in gate-drain region, in order for the pre-stress conditions to be recovered, as the stress bias is removed. The hole emission process from  $C_N$  states has time constants in the order of hundreds of seconds at

room temperature [14], [15]. Therefore, after each stress step, a full recovery from degradation cannot be achieved within the 300-s unbiased phase. As a result, degradation accumulates leading to an increasing  $g_m$  drop, especially in the high  $V_{GS}$  regime, see Fig. 2(b). The negligible  $V_T$  drift observed during the OFF-state tests indicates that no significant charge build-up occurs below the gated region of the device. This result can also be interpreted with the 'hole-redistribution' model as being due to the complete charge redistribution below the gate contact following the unbiased phase after each stress step. This point is further clarified in Sec. IV.

3

Results in Fig. 3 indicate a more pronounced degradation after ON-state stress compared to the OFF-state case. Moreover, not only  $g_{m,max}$  incrementally decreases after each stress step but also  $V_{\rm T}$  drifts significantly. At  $V_{\rm GS,STR} = 0$  V, significant current flow occurs in the channel, and energetic electrons can acquire enough energy to spill over to the buffer. When significant electron injection occurs in the C-doped buffer, the unoccupied C<sub>N</sub> states can easily trap injected electrons, resulting in an increased negatively ionized trap density, in turn resulting in reduced 2DEG conductivity [16], [17]. Depending on whether electron trapping happens below the gate or/and in the gate-to-drain access region, a  $V_{\rm T}$  increase or a  $g_{m,max}$  drop, or both effects, is/are induced [5], [18]. Both parameters are found to degrade in Fig. 3, indicating that CHE injection must have interested both buffer regions. This hypothesis is further confirmed by the fact that this degradation is non-recoverable and that accumulates over each stress step, see Fig. 3. In fact, under negligible electron injection conditions in the buffer (as in the OFF-state case considered above) C<sub>N</sub> states act as hole traps, i.e. they change their charge state by interacting with the valence band (emitting and capturing holes) [14]. Instead, when significant electron injection occurs (as in the ON-state case) C<sub>N</sub> states can act as electron traps. The significant energy depth of this level with respect to the conduction band renders the emission of the trapped electrons virtually impossible by simple thermal emission at room temperature. From this, one can deduce that electron trapping into C<sub>N</sub> states gives rise to a semi-permanent degradation. Recovery from this phenomenon can only be achieved by applying a high-temperature recovery step and/or by shining UV light to enhance electron emission from traps or generate an excess of holes to promote electron-hole recombination within the traps.

It is important to highlight that both OFF- and ON-state degradation effects observed in the step-stress experiments shown here are peculiar of C-doped devices. Even in Fe-doped devices the negative charge stored within the buffer increases during both OFF-state and ON-state stress [9]. This happens as a result of electron trapping into the Fe-related acceptor traps at 0.56 eV from the conduction band. However, in the case of Fe doping, an unbiased phase of 300 s following each stress step is long enough to completely revert this process, thanks to the  $\approx$ 10-ms time constant characterizing electron emission to the conduction band from the Fe states [19].

We eventually point out that the ON-state stress results presented here do not contradict the 'hole-redistribution' model, as in fact this model can only be applied for stress bias conditions under which C doping is able to effectively avoid

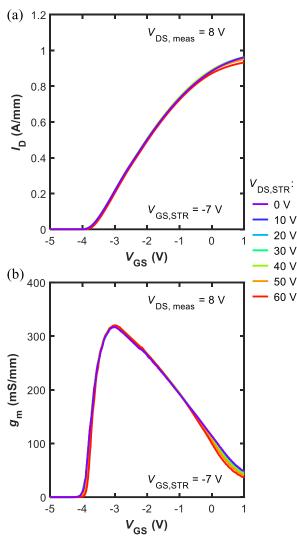

Fig. 4. Simulated (a) drain-current ( $I_D$ ) and (b) transconductance ( $g_m$ ) vs gate-source-voltage ( $V_{GS}$ ) curves prior to stress (0 V curve) and after 120-s OFF-state stress, i.e.,  $V_{GS,STR} = -7$  V,  $V_{DS,STR} = 10-60$  V, followed by 300-s recovery at (0, 0) V.

significant electron injection from the source and/or from the substrate into the buffer [14].

# **IV. STRESS SIMULATIONS**

To validate the hypothesis regarding the physical mechanisms formulated in Sec. III. two-dimensional (2D) numerical device simulations were performed with the SDevice<sup>TM</sup> simulator [20]. To take hot electron effects into account in a more accurate way, charge transport was modelled by means of the hydrodynamic equations. Other models (piezoelectric polarization charge, trap dynamics, etc.) were employed analogously to what done in our previous works [21]. C doping in the GaN buffer was modeled by considering a dominant deep acceptor trap at 0.9 eV above  $E_{\rm V}$  partially compensated by a shallow donor trap at 0.11 eV below  $E_{\rm C}$  [22]. The adopted C doping model, described more in detail in [22], is consistent with the current understanding of the energy levels associated with C introduction into GaN [23]. described succinctly as follows. While early DFT calculations based on LDA and GGA approximations predicted the substitutional C<sub>N</sub> state to be a shallow acceptor [24], more accurate DFT calculations using the HSE functional

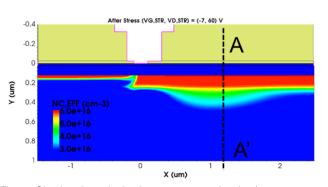

Fig. 5. Simulated net ionized acceptor trap density ( $N_{C,EFF} = N_{ACC}^{-} - N_{DON}^{+}$ ) immediately after stress (i.e., prior to recovery) under OFF-state stress, i.e., ( $V_{GS,STR}$ ,  $V_{DS,STR}$ ) = (-7, 60) V. Cutline A-A' used in Figs. 6 and 7 is indicated.

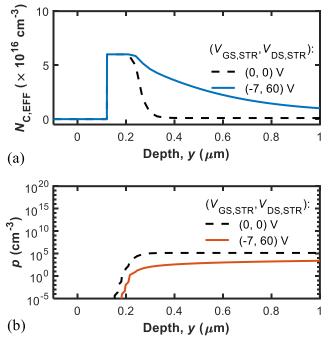

Fig. 6. Simulated (a)  $N_{C,EFF}$  and (b) *p* along the vertical cutline A-A' (see Fig. 5) prior to and after OFF-state stress. Increase of  $N_{C,EFF}$  near the surface of the buffer (i.e., near the channel/buffer interface) correlates with depletion region widening and consequent hole emission from traps.

consistently predicted the  $C_N$  acceptor level in the 0.9-1.1 eV range above the valence band maximum [25]. This is in good agreement with extensive experimental findings, including *(i)* measurement of thermally activated reduction in the resistivity of carbon-doped GaN [26]; *(ii)* observation of p-type conductivity and its thermal activation energy [27]; *(iii)* a hole trap detection by DLTS and minority carrier transient spectroscopy [28]; *(iv)* results from photocapacitance, pulsed photoionization, and DLOS [29]; *(v)* yellow luminescence studies [28], [30].

The adopted active trap concentrations were  $8 \times 10^{16}$  cm<sup>-3</sup> and  $2 \times 10^{16}$  cm<sup>-3</sup>, for C-related acceptors and donors, respectively. Poole-Frenkel enhancement of hole emission from acceptor traps was included in the setup [15].

To provide insight into the observed degradation effects, we mimicked measurement conditions as follows.  $V_{GS}$  and  $V_{DS}$  were kept constant to their stress values for 120 s at each ( $V_{GS,STR}$ ,  $V_{DS,STR}$ ) condition. Recovery was performed after stress for 300

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 License. For more information, see https://creativecommons.org/licenses/bv-nc-nd/4.0/

Fig. 7. Simulated band diagrams along the vertical cutline A-A' (see Fig. 5): (a) at (0, 0) V, (b) at the end of the 120-s stress at (-7, 60) V and (c) at the end of the subsequent 300-s rest phase at (0, 0) V. Stress increases the depletion region width at channel/buffer interface which is not completely recovered after the 300-s phase, leading to the  $g_m$  drop shown in Fig. 4.

s by grounding gate and drain contacts (source and substrate where grounded during the whole simulation).  $I_{\rm D}$ - $V_{\rm GS}$  curves at  $V_{\rm DS} = 8$  V were acquired after the recovery interval was completed. Ramp time during  $I_{\rm D}$ - $V_{\rm GS}$  acquisition was 1 s.

Notice that for ensuring convergence of the simulations, the stress steps could not be applied sequentially one after the other. Moreover, since the focus of this work is on the impact of buffer traps on degradation, trapping in the passivation layer was not included in the simulation setup, which however might contribute to the total degradation after ON-state stress [31]. For these reasons, the simulations tend to underestimate the total amount of degradation compared to the actual data. Nevertheless, simulation results still allow to obtain a clear picture of the physical mechanisms taking place in the buffer during stress and as such the adopted simplification does not affect the intepretation.

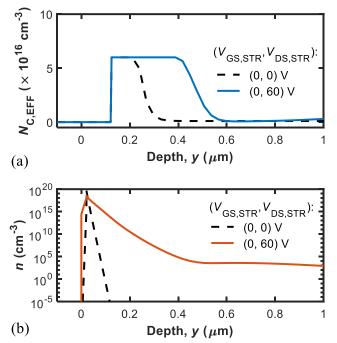

Figure 4 shows the simulation results under the OFF-state in terms of  $I_{\rm D}$ - and  $g_{\rm m}$ - $V_{\rm GS}$  curves. These curves are taken up to  $V_{\text{DS,STR}} = 60 \text{ V}$  with 10-V step. At first glance one can see how simulations allow to qualitatively reproduce the experimental features related to OFF-state step stress. Particularly, Fig. 4 shows a small  $g_{m,max}$  degradation, a more appreciable  $g_m$  drop at high  $V_{GS}$  and a negligible  $V_T$  shift, in agreement with experiments illustrated in Fig. 2. Figure 5 shows the contour plot of net ionized trap concentration  $(N_{C,EFF})$  in the OFF-state stress condition taken right after 120-s of stress at  $V_{\text{DS}} = 60 \text{ V}$ . As it can be seen in Fig. 5, under OFF-state stress the negative charge buildup due to C<sub>N</sub> acceptors extends through the upper portion of the gate-drain region and is correlated to the depletion of holes (emitted by the traps). This is further shown in Fig. 6, which plots  $N_{\text{C,EFF}}$  and the free hole density (p) along the cutline A-A' shown in Fig. 5 in the gate-drain access region.

5

Fig. 8. Simulated (a) drain-current ( $I_D$ ) and (b) transconductance ( $g_m$ ) vs gate-source-voltage ( $V_{GS}$ ) curves prior to stress (0 V curve) and after 120-s ON-state stress, i.e.,  $V_{GS,STR} = 0$  V,  $V_{DS,STR} = 10-60$  V, followed by 300-s recovery at (0, 0) V.

As it can be noted, N<sub>C,EFF</sub> increases compared to the pre-stress conditions and simultaneously p decreases, confirming that the negative charge buildup is due to hole emission following the depletion region widening. Figure 7 shows the band diagram along the same A-A' cutline used in Fig. 6, (a) at (0, 0) V bias prior to stress application, (b) at the end of the 120-s stress phase at (-7, 60) V and (c) at the end of the subsequent 300-s rest phase at (0, 0) V. The OFF-state stress increases the depletion region in the buffer as indicated by the enlargement and widening of the upward band bending in Fig. 7(b), compared to the pre-stress conditions illustrated by Fig. 7(a). During the subsequent 300-s rest phase at (0, 0) V, the buffer depletion region shrinks but does not recover to pre-stress conditions, as it can be appreciated by comparing Fig. 7(c) with Fig. 7(a). This incomplete recovery explains the cumulative effect of stress steps in terms of the increasing  $g_{\rm m}$  drop as observed in the measurements, see Fig. 2(b).

Figure 8 shows the simulated  $I_{\rm D}$ - and  $g_{\rm m}$ - $V_{\rm GS}$  curves after ONstate stress. Simulation results show a positive  $V_{\rm T}$  shift, in agreement with the experimental findings shown in Fig. 3. However, simulations underestimate the degradation of  $g_{\rm m,max}$

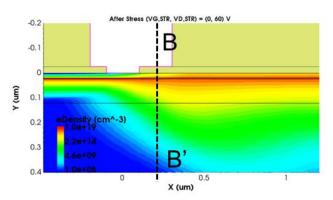

Fig. 9. Simulated electron density (*n*) immediately after stress (i.e., prior to recovery) under ON-state stress, i.e.,  $(V_{GS,STR}, V_{DS,STR}) = (0, 60)$  V. Cutline B-B' used in Fig. 9 is indicated.

Fig. 10. Simulated (a)  $N_{C,EFF}$  and (b) *n* along the vertical cutline B-B' (see Fig. 9) prior to and after ON-state stress. Increase of  $N_{C,EFF}$  near the surface of the buffer (i.e., near the channel/buffer interface) correlates with electron injection in the same region from the 2DEG.

compared to the experimental data in Fig. 3; we attribute this discrepancy to the neglected hot electrons trapping at the device surface and in the passivation which can contribute to the total degradation [31]. Hot electrons can also be trapped in the AlGaN bulk and at AlGaN/GaN interface.

Figure 9 shows shows the contour plot of the free electron density (*n*) in the ON-state stress condition taken right after stress 120-s of stress at  $V_{\rm DS} = 60$  V. In this case, the degradation observed in Fig. 8 can be understood as being due to the injection of electrons into the buffer, as clearly shown in Fig. 9. Figure 10 further confirms the correlation between the negative charge build-up with the electron injection in the buffer during ON-state stress, by showing  $N_{\rm C,EFF}$  and *n* along the cutline B-B' (indicated in Fig. 9). In this case,  $N_{\rm C,EFF}$  below the gate increases during stress due to trapping of the hot electrons injected from the channel.

## V. RECOVERY EXPERIMENTS

To confirm the validity of the interpretation we carried out three types of recovery experiments on DUTs previously subjected to OFF-state or ON-state step-stress tests (described in Section III). These recovery experiments were carried out undeer the following conditions: *i*) long term (42 days) at room temperature; *ii*) short term at high-temperature (150 and 200 °C); *iii*) with UV-illumination (385, 365, and 265 nm) for 5 minutes.

Figure 11 shows the results of these analyses. After long term (42 days) storage at room temperature, DUTs subjected to OFFstate step stress showed complete recovery, see Fig. 11(a) and (b). Full recovery is consistent with the redistribution (and recapture) of holes first emitted during stress [14]. Since full

Fig. 11. (a, c) Drain-current ( $I_D$ ) and (b, d) transconductance ( $g_m$ ) vs gate-source-voltage ( $V_{GS}$ ) curves measured after long term (42 days) recovery at room temperature on DUTs subjected to OFF-state (a, b) and ON-state (c, d) step-stress. (e) Short term, high temperature and with UV-illumination recovery of  $g_m - V_{GS}$  carried out on DUTs subjected to ON-state step stress.

6

recovery was achieved at room temperature, experiments of type *ii*) and *iii*) were not carried out on devices stressed under OFF-state.

Conversely, DUTs subjected to ON-state step stress showed, after long term (42 days) room temperature storage, only partial recovery that mainly involved  $g_{m,max}$  and high-current  $g_m$ , whereas  $V_T$  did not recover, see Fig. 11(c), (d). The partial recovery can be attributed to electron de-trapping from traps located at the device surface and/or in the passivation [31], whereas the remaning  $g_m$  degradation and lack of  $V_T$  recovery can be attributed to the hot electrons trapped in the C-related buffer traps.

Figure 11(e) shows the results of the recovery experiments corresponding to cases *ii*) and *iii*), explained in the following. The short-term high temperature storage induces an almost complete  $g_{m,max}$  recovery, due to a combination of thermal detrapping of electrons from surface traps and accelerated redistribution of holes within the buffer [14]. The recovery experiments with UV-illumination led to complete  $g_{m,max}$  recovery but no  $V_T$  recovery. This can be explained by the fact that the region under the gate contact is shielded from the photon flux by the gate and field plate metal, and as such the UV-illumination is not effective in assisting electron detrapping from C<sub>N</sub> traps located in this region. In other words, the C-related buffer traps under the gate remain negatively charged causing a non-recoverable positive  $V_T$  shift even under UV illumination.

## VI. CONCLUSIONS

We presented results from drain step stress tests on 0.15- $\mu$ m AlGaN/GaN HEMTs fabricated on wafers with C-doped buffer layers. Both OFF- and ON-state stress conditions were applied, finding a small  $g_m$  drop in the first case, whereas an enhanced  $g_m$  drop and positive  $V_T$  shift in the second one. Twodimensional hydrodynamic device simulations were carried out as an aid in the interpretation of the results. Recovery experiments were also carried out at room-temperature, high temperature and under UV illumination.

Based on both stress and recovery experiments as well as on simulations, we conclude that:

1) The  $g_m$  drop under OFF-state stress conditions can be interpreted with the 'hole-redistribution' model as being due to hole emission from the  $C_N$  acceptor traps leading to increased negative charge stored in the gate-drain access region. The latter can accumulate during the step stress experiment as a result of the long time constants involved. Room-temperature storage of the DUT was found to induce a total recovery of stress effects, which is compatible with the 'hole-redistribution' model.

2) Both  $g_m$  and  $V_T$  degradation under ON-state stress conditions can be attributed to capture of CHEs by  $C_N$  traps in the buffer and by surface traps, inducing negative charge buildup in the buffer under the gate and within the gate-drain access region both in the buffer and at the surface. Long-term, room-temperature storage caused small recovery from  $g_m$ degradation, which can be attributed to electron de-trapping from surface traps. High-temperature and UV-illumination recovery experiments instead allowed almost complete recovery of  $g_m$  but not of  $V_T$ . Surface electron traps can effectively be depleted by the high-temperature storage, while  $C_N$  buffer acceptor traps in the gate-drain access region emit the trapped electrons with the aid of UV-illumination. Conversely, the region under the gate is shielded by the metal and UV-illumination is not effective in depleting the negative charge build-up due to electron trapping in  $C_N$  buffer states, explaining the permanent degradation of  $V_T$ .

7

Owing to the peculiarity of C doping, when  $C_N$  acceptors, that "naturally" behave as hole traps, are forced to capture electrons, as it can happen under ON-state conditions because of CHE injection into the buffer, the resulting negative charge buildup can appear permanent and be misinterpreted as a structural damage. This phenomenon should be characterized during the device-technology development and specifically taken into consideration, especially in short-gate HEMTs for high-frequency applications, for the optimization of C doping or the selection of the most suitable epitaxy, in order to properly trade off breakdown-voltage increase with tolerable, overall trapping effects.

#### REFERENCES

[1]K. Yuk, G. R. Branner, and C. Cui, "Future directions for GaN in 5G and satellite communications," in *Midwest Symposium on Circuits and Systems*, 2017, vol. 2017-Augus, pp. 803–806. doi: 10.1109/MWSCAS.2017.8053045.

[2]S. Nakajima, "GaN HEMTs for 5G Base Station Applications," in *IEEE International Electron Devices Meeting (IEDM)*, 2018, p. 14.2.1-14.2.4. doi: 10.1109/IEDM.2018.8614588.

[3]U. K. Mishra, L. Shen, T. E. Kazior, and Y. F. Wu, "GaN-based RF power devices and amplifiers," *Proceedings of the IEEE*, vol. 96, no. 2, pp. 287–305, 2008, doi: 10.1109/JPROC.2007.911060.

[4] W. Chen, R. A. Chinga, S. Yoshida, J. Lin, C. Chen, and W. Lo, "A 25.6 W 13.56 MHz wireless power transfer system with a 94% efficiency GaN Class-E power amplifier," in *IEEE MTT-S International Microwave Symposium Digest*, 2012, pp. 56–58. doi: 10.1109/MWSYM.2012.6258349.

[5]M. Meneghini, C. De Santi, I. Abid, M. Buffolo, M. Cioni, R. A. Khadar, L. Nela, N. Zagni, A. Chini, F. Medjdoub, G. Meneghesso, G. Verzellesi, E. Zanoni, and E. Matioli, "GaN-based power devices: Physics, reliability, and perspectives," *Journal of Applied Physics*, vol. 130, no. 18, p. 181101, Nov. 2021, doi: 10.1063/5.0061354.

[6]M. J. Uren, J. Moreke, and M. Kuball, "Buffer design to minimize current collapse in GaN/AlGaN HFETs," *IEEE Transactions on Electron Devices*, vol. 59, no. 12, pp. 3327–3333, 2012, doi: 10.1109/TED.2012.2216535.

[7]E. Bahat-Treidel, F. Brunner, O. Hilt, E. Cho, J. Würfl, and G. Trankle, "AlGaN/GaN/GaN:C back-barrier HFETs with breakdown voltage of over 1 kV and low RON× A," *IEEE Transactions on Electron Devices*, vol. 57, no. 11, pp. 3050–3058, Nov. 2010, doi: 10.1109/TED.2010.2069566.

[8]M. J. Uren and M. Kuball, "Impact of carbon in the buffer on power switching GaN-on-Si and RF GaN-on-SiC HEMTs," *Japanese Journal of Applied Physics*, vol. 60, no. SB, p. SB0802, 2021, doi: 10.35848/1347-4065/abdb82.

[9]C. De Santi, E. Zanoni, M. Meneghini, G. Meneghesso, F. Rampazzo, V. Z. Gao, C. Sharma, F. Chiocchetta, G. Verzellesi, A. Chini, M. Cioni, N. Zagni, C. Lanzieri, A. Pantellini, M. Peroni, and L. Latessa, "Role of carbon in dynamic effects and reliability of 0.15-um AlGaN/GaN HEMTs for RF power amplifiers," in *Gallium Nitride Materials and Devices XVII*, San Francisco, United States, Mar. 2022, p. 56. doi: 10.1117/12.2609666.

[10] J. A. del Alamo and E. S. Lee, "Stability and Reliability of Lateral GaN Power Field-Effect Transistors," *IEEE Transactions on Electron Devices*, vol. 66, no. 11, pp. 4578–4590, Nov. 2019, doi: 10.1109/TED.2019.2931718.

[11] M. J. Uren, S. Karboyan, I. Chatterjee, A. Pooth, P. Moens, A. Banerjee, and M. Kuball, "Leaky Dielectric' Model for the Suppression of Dynamic \$R\_{mathrm{ON}}\$ in Carbon-Doped AlGaN/GaN HEMTs," *IEEE Transactions on Electron Devices*, vol. 64, no. 7, pp. 2826–2834, Jul. 2017, doi: 10.1109/TED.2017.2706090.

[12] D. Bisi, M. Meneghini, F. A. Marino, D. Marcon, S. Stoffels, M. Van Hove, S. Decoutere, G. Meneghesso, and E. Zanoni, "Kinetics of Buffer-Related RON-Increase in GaN-on-Silicon MIS-HEMTs," *IEEE Electron Device Letters*, vol. 35, no. 10, pp. 1004–1006, Oct. 2014, doi: 10.1109/LED.2014.2344439.

[13] G. Meneghesso, M. Meneghini, I. Rossetto, D. Bisi, S. Stoffels, M. Van Hove, S. Decoutere, and E. Zanoni, "Reliability and parasitic issues in GaNbased power HEMTs: a review," *Semiconductor Science and Technology*, vol. 31, no. 9, p. 093004, Sep. 2016, doi: 10.1088/0268-1242/31/9/093004.

[14] N. Zagni, A. Chini, F. M. Puglisi, M. Meneghini, G. Meneghesso, E. Zanoni, P. Pavan, and G. Verzellesi, "Hole Redistribution' Model Explaining the Thermally Activated  $R_{ON}$  Stress/Recovery Transients in Carbon-Doped AlGaN/GaN Power MIS-HEMTs," *IEEE Trans. Electron Devices*, vol. 68, no. 2, pp. 697–703, Feb. 2021, doi: 10.1109/TED.2020.3045683.

[15] N. Zagni, M. Cioni, F. Iucolano, M. Moschetti, G. Verzellesi, and A. Chini, "Experimental and numerical investigation of Poole–Frenkel effect on dynamic R <sub>ON</sub> transients in C-doped p-GaN HEMTs," *Semicond. Sci. Technol.*, vol. 37, no. 2, p. 025006, Feb. 2022, doi: 10.1088/1361-6641/ac4113.

[16] S. Dutta Gupta, V. Joshi, R. R. Chaudhuri, and M. Shrivastava, "Part I: Physical Insights Into Dynamic R ON Behavior and a Unique Time-Dependent Critical Stress Voltage in AlGaN/GaN HEMTs," *IEEE Transactions on Electron Devices*, vol. 68, no. 11, pp. 5720–5727, Nov. 2021, doi: 10.1109/TED.2021.3109847.

[17] S. Dutta Gupta, V. Joshi, R. R. Chaudhuri, and M. Shrivastava, "Unique Gate Bias Dependence of Dynamic ON-Resistance in MIS-Gated AlGaN/GaN HEMTs and Its Dependence on Gate Control Over the 2-DEG," *IEEE Transactions on Electron Devices*, vol. 69, no. 3, pp. 1608–1611, Mar. 2022, doi: 10.1109/TED.2022.3144378.

[18] D. Bisi, M. Meneghini, M. Van Hove, D. Marcon, S. Stoffels, T.-L. L. Wu, S. Decoutere, G. Meneghesso, and E. Zanoni, "Trapping mechanisms in GaN-based MIS-HEMTs grown on silicon substrate," *physica status solidi (a)*, vol. 212, no. 5, pp. 1122–1129, May 2015, doi: 10.1002/pssa.201431744.

[19] M. Cioni, N. Zagni, L. Selmi, G. Meneghesso, M. Meneghini, E. Zanoni, and A. Chini, "Electric Field and Self-Heating Effects on the Emission Time of Iron Traps in GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 68, no. 7, pp. 3325–3332, Jul. 2021, doi: 10.1109/TED.2021.3081613.

[20] Synopsys, "Sentaurus SDevice Manual (S-2021.06)." 2021.

[21] M. Cioni, N. Zagni, F. Iucolano, M. Moschetti, G. Verzellesi, and A. Chini, "Partial Recovery of Dynamic  $R_{ON}$  Versus OFF-State Stress Voltage in p-GaN Gate AlGaN/GaN Power HEMTs," *IEEE Trans. Electron Devices*, vol. 68, no. 10, pp. 4862–4868, Oct. 2021, doi: 10.1109/TED.2021.3105075.

[22] N. Zagni, A. Chini, F. M. Puglisi, P. Pavan, and G. Verzellesi, "On the Modeling of the Donor/Acceptor Compensation Ratio in Carbon-Doped GaN to Univocally Reproduce Breakdown Voltage and Current Collapse in Lateral

GaN Power HEMTs," *Micromachines*, vol. 12, no. 6, p. 709, Jun. 2021, doi: 10.3390/mi12060709.

8

[23] F. Zimmermann, J. Beyer, C. Röder, F. C. Beyer, E. Richter, K. Irmscher, and J. Heitmann, "Current Status of Carbon-Related Defect Luminescence in GaN," *physica status solidi (a)*, vol. 218, no. 20, p. 2100235, 2021, doi: 10.1002/pssa.202100235.

[24] A. F. Wright, "Substitutional and interstitial carbon in wurtzite GaN," *Journal of Applied Physics*, vol. 92, no. 5, pp. 2575–2585, 2002, doi: 10.1063/1.1498879.

[25] J. L. Lyons, A. Janotti, and C. G. Van De Walle, "Carbon impurities and the yellow luminescence in GaN," *Applied Physics Letters*, vol. 97, no. 15, 2010, doi: 10.1063/1.3492841.

[26] E. Richter, F. C. Beyer, F. Zimmermann, G. Gärtner, K. Irmscher, I. Gamov, J. Heitmann, M. Weyers, and G. Tränkle, "Growth and Properties of Intentionally Carbon-Doped GaN Layers," *Crystal Research and Technology*, vol. 55, no. 2, p. 1900129, 2020, doi: 10.1002/crat.201900129.

[27] M. Iwinska, R. Piotrzkowski, E. Litwin-Staszewska, T. Sochacki, M. Amilusik, M. Fijalkowski, B. Lucznik, and M. Bockowski, "Highly resistive C-doped hydride vapor phase epitaxy-GaN grown on ammonothermally crystallized GaN seeds," *Appl. Phys. Express*, vol. 10, no. 1, p. 011003, Dec. 2016, doi: 10.7567/APEX.10.011003.

[28] U. Honda, Y. Yamada, Y. Tokuda, and K. Shiojima, "Deep levels in n-GaN doped with carbon studied by deep level and minority carrier transient spectroscopies," *Japanese Journal of Applied Physics*, vol. 51, no. 4 PART 2, Apr. 2012, doi: 10.1143/JJAP.51.04DF04.

[29] A. Hierro, D. Kwon, S. A. Ringel, M. Hansen, J. S. Speck, U. K. Mishra, and S. P. DenBaars, "Optically and thermally detected deep levels in n-type Schottky and p+-n GaN diodes," *Applied Physics Letters*, vol. 76, no. 21, pp. 3064–3066, May 2000, doi: 10.1063/1.126580.

[30] H. Yamada, H. Chonan, T. Takahashi, T. Yamada, and M. Shimizu, "Deep-level traps in lightly Si-doped n-GaN on free-standing m-oriented GaN substrates," *AIP Advances*, vol. 8, no. 4, p. 045311, Apr. 2018, doi: 10.1063/1.5011362.

[31] N. Modolo, C. De Santi, A. Minetto, L. Sayadi, S. Sicre, G. Prechtl, G. Meneghesso, E. Zanoni, and M. Meneghini, "A Physics-Based Approach to Model Hot-Electron Trapping Kinetics in p-GaN HEMTs," *IEEE Electron Device Letters*, vol. 42, no. 5, pp. 673–676, May 2021, doi: 10.1109/LED.2021.3067796.