## Università degli Studi di Modena e Reggio Emilia

DIPARTIMENTO DI INGEGNERIA "ENZO FERRARI" DI MODENA Corso di Dottorato di Ricerca in "Information and Communication Technologies (ICT)"

CICLO XXXIII

# SIMULATION AND MODELING METHODS FOR PREDICTING PERFORMANCE AND RELIABILITY LIMITS OF 21<sup>ST</sup>-CENTURY ELECTRONICS

Candidato: Relatore:

Dott. Nicolò Zagni Prof. Paolo Pavan

Correlatore:

Prof. Francesco Maria Puglisi

Coordinatore Dottorato:

Prof. Sonia Bergamaschi

Davanti c'era la menzogna comprensibile, e dietro, l'incomprensibile verità M. Kundera

# **Acknowledgments**

There are quite a few people to thank for helping me successfully reaching the end of the PhD journey.

- My deepest gratitude goes to professor Paolo Pavan, who introduced me to the research

process as my Master's Thesis advisor first and as my PhD supervisor then. His valuable

advices and most of all his guidance were very important to me to reach this point,

that I could not reach otherwise.

- I thank professor Francesco Maria Puglisi, and I gladly acknowledge the many hours spent in the lab with him doing experiments or discussing on many different research topics. His expertise and enthusiasm were very inspiring to me.

- Many thanks are devoted to professor Giovanni Verzellesi, who shared with me his vast knowledge of semiconductor physics and other (not always technical) topics, helping me most of all in understanding and appreciating the nuances of device simulations.

- I acknowledge the fruitful collaboration with professor Alessandro Chini, that offered me

his challenging perspective on Gallium Nitride devices and on the issues dealing with 'real

devices' compared to those encountered in the simulations.

- I deeply thank professor Muhammad Ashraful Alam from Purdue University, whom I started working with as 'visiting scholar' in summer 2018 and 2019. He is a great advisor and one of the most recognized mentors in the electron devices field. Working with him allowed me to grow substantially and made me capable of bringing new perspectives to my work.

• I thank prof. Susanna Reggiani (University of Bologna) and prof. David Esseni (University of Udine) for evaluating and reviewing this Thesis.

I also gladly acknowledge my fellow PhD students in Modena, whom I shared with many hours in the lab. They all made my experience more enjoyable. I also thank all the (past and present) Alam's group members at Purdue University that I was very lucky to meet, in the hope that our paths will cross again.

On the personal side, I want to thank my girlfriend Giulia for her support and understanding even when we were physically far away. Needless to say, it was a painful process and of countless hours spent in the lab, taken away from friends and family. I appreciated their patience and understanding for the many occasions that I sacrificed spending time with them to work. This thesis is dedicated to all of you.

## **Abstract**

In recent years, a plethora of novel semiconductor devices have started emerging as worthy heirs of Silicon-based transistors – giving rise to the 'post-Moore' era. Traditional electronics is mostly based on Si devices, – from logic to memory, to high frequency/power and sensing applications – but this paradigm is changing thanks to the developments in different fields ranging from physics and semiconductor materials, to processing techniques and computing architectures. In this hectic new scenario, before even considering a new technology as a replacement of the existing ones, the limiting factors to its performance and reliability need to be well-understood and engineered for. In this sense, simulations and physics-based modeling represent critical tools to make sure that newly conceived technologies stand up to the requirements of 21<sup>st</sup> century electronics.

In this thesis, state-of-the-art simulation and compact modeling tools are exploited to analyze the performance and reliability limits of several emerging technologies. Specifically, this dissertation is focused on four application scenarios and the relative candidate technologies that aim to providing enhanced performance/reliability compared to Si-based counterparts. These are: *i*) III-V MOSFETs for logic/digital circuits, *ii*) resistive-RAMs and ferroelectric-FETs for non-volatile memory and in-memory computing, *iii*) GaN-based high-speed transistors for power applications, and *iv*) negative capacitance transistors for biosensing.

# Sommario

Negli ultimi anni si è visto emergere una pleteora di dispositivi a semiconduttore innovativi, candidati a essere degni eredi dei transistor basati su Silicio e dando via alla cosidetta era 'post-Moore'. Infatti, nonostante l'elettronica tradizionale sia basata su dispositivi in Silicio, – dai circuiti logici alle memorie, dalle applicazioni ad alta frequenza/potenza alla sensoristica – questo paradigma sta mutando grazie agli sviluppi provenienti da diversi campi di ricerca, dalla fisica e dai materiali a semiconduttore sino alle tecniche di fabbricazione e le architetture dei calcolatori. In questo nuovo, frenetico scenario, i potenziali fattori limite delle performance e dell'affidabilità di nuovi dispositivi devono essere ben compresi in una fase relativamente preliminare dello sviluppo affinché essi possano essere effettivamente presi in considerazione come potenziali sostituti della tecnologia esistente. In questo senso, la simulazione e la modellizzazione fisica rappresentano degli strumenti fondamentali per la comprensione e dunque la progettazione di nuove tecnologie per soddisfare i requisiti dell'elettronica del XXI secolo.

In questa tesi vengono presentati dei metodi di simulazione numerica e di modellizzazione compatta allo stato dell'arte per analizzare i limiti delle performance e dell'affidabilità di differenti tecnologie emergenti. Nello specifico, questa tesi affronta quattro differenti scenari applicativi e le tecnologie corrispondenti candidate come possibili sostituti delle controparti in Silicio. Queste sono: *i)* III-V MOSFETs per circuiti logici/digitali, *ii)* resitive-RAMs e ferroelectric-FETs per memorie non-volatili e elaborazione in-memory, *iii)* transistor ad alta velocità basati su GaN per applicazioni di potenza, e *iv)* transistor a capacità negativa per biosensori.

# **Contents**

| Acknowledgments |                                               |         |                                               |     |  |  |

|-----------------|-----------------------------------------------|---------|-----------------------------------------------|-----|--|--|

| Al              | Abstract                                      |         |                                               |     |  |  |

| So              | mma                                           | rio     |                                               | v   |  |  |

| Li              | st of A                                       | Acronyr | ns                                            | X   |  |  |

| Li              | st of S                                       | Symbols | 5                                             | xvi |  |  |

| 1               | Intr                                          | oductio | n                                             | 1   |  |  |

|                 | 1.1                                           | Semico  | onductor Device Simulation and Modeling       | 4   |  |  |

|                 |                                               | 1.1.1   | Process Simulation                            | 5   |  |  |

|                 |                                               | 1.1.2   | Device Simulation                             | 6   |  |  |

|                 |                                               | 1.1.3   | Drift-Diffusion Equations                     | 9   |  |  |

|                 |                                               | 1.1.4   | Circuit Simulation and Compact Modeling       | 11  |  |  |

|                 | 1.2                                           | Outline | e                                             | 12  |  |  |

| Re              | eferen                                        | ces – C | hapter 1                                      | 13  |  |  |

| 2               | Traps and Variability Issues in III-V MOSFETs |         |                                               |     |  |  |

|                 | 2.1                                           | Scaling | g of Logic Transistors — III-Vs to the rescue | 16  |  |  |

|                 | 2.2                                           | Backg   | round                                         | 17  |  |  |

|                 |                                               | 2.2.1   | InGaAs Properties                             | 17  |  |  |

|    |        | 2.2.2    | Quantum Correction to Carrier Density in Ultra-Scaled Devices              | 18 |

|----|--------|----------|----------------------------------------------------------------------------|----|

|    |        | 2.2.3    | InGaAs MOSFET Architectures                                                | 19 |

|    |        | 2.2.4    | Simulation Approaches                                                      | 20 |

|    |        | 2.2.5    | Effects and Signatures of ITs and BTs                                      | 22 |

|    |        | 2.2.6    | Variability in Nanoscale MOSFETs                                           | 23 |

|    | 2.3    | Contrib  | oution: Mobility Measurements Inaccuracies due to ITs and BTs in planar    |    |

|    |        | InGaA    | s MOSFETs                                                                  | 25 |

|    |        | 2.3.1    | Calibration of $I$ – $V$ and $C$ – $V$ characteristics                     | 26 |

|    |        | 2.3.2    | Effects of ITs and BTs on Mobility Extraction                              | 28 |

|    |        | 2.3.3    | Conclusions                                                                | 30 |

|    | 2.4    | Contrib  | oution: Statistical Variability in Ultra-scaled Double-Gate InGaAs MOSFETs | 31 |

|    |        | 2.4.1    | Assessing Variability in TCAD with the Statistical Impedance Field Method  | 31 |

|    |        | 2.4.2    | Variability Sources Modeling                                               | 32 |

|    |        | 2.4.3    | Threshold Voltage Variability and its Sensitivity to Critical Design Pa-   |    |

|    |        |          | rameters in InGaAs DG-UTB MOSFETs                                          | 34 |

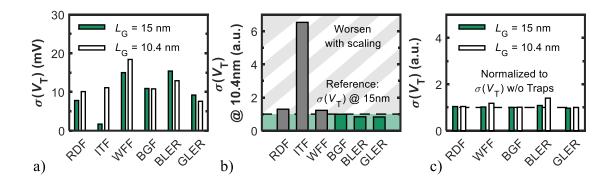

|    |        | 2.4.4    | Impact of Traps on Variability                                             | 39 |

|    |        | 2.4.5    | Conclusions                                                                | 44 |

| Re | eferen | ces – Cl | napter 2                                                                   | 46 |

| 3  | Com    | pact M   | odeling of Noise and Aging in Emerging Non-Volatile Memories               | 54 |

|    | 3.1    | NVMs     | to Tear Down the Memory Wall                                               | 55 |

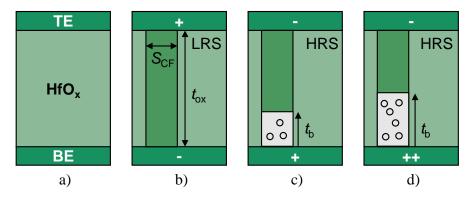

|    | 3.2    | Backgr   | round – Elements of RRAM Physics                                           | 57 |

|    | 3.3    | Contrib  | oution: Exploiting Noise in RRAMs to Design Advanced Circuit Applications  | 60 |

|    |        | 3.3.1    | RTN Compact Model in HRS and LRS                                           | 61 |

|    |        | 3.3.2    | Model Validation                                                           | 67 |

|    |        | 3.3.3    | Application: Random Number Generator                                       | 69 |

|    |        | 3.3.4    | Conclusions                                                                | 70 |

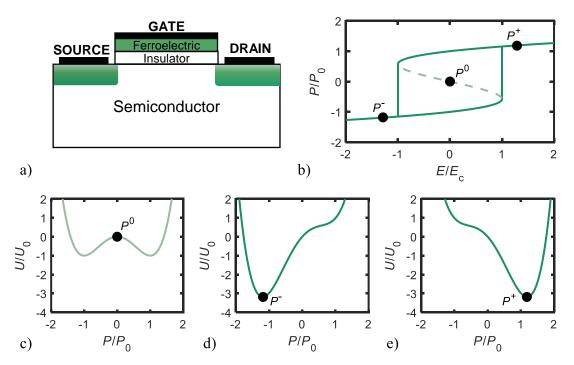

|    | 3.4    | Backgr   | round – Basics of FeFET Physics                                            | 71 |

|    |        | 3.4.1    | Ferroelectric Polarization Loop Description with Landau Theory             | 72 |

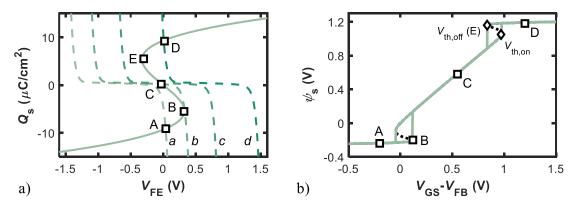

|   |                                                          | 3.4.2                                                                     | MFS Structure Analysis                                               | 74  |

|---|----------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------|-----|

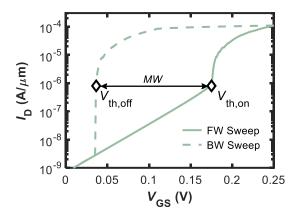

|   | 3.5                                                      | 3.5 Contribution: Endurance Limits Evaluation in FeFETs with Memor        |                                                                      |     |

|   |                                                          | Analyt                                                                    | ic Expression                                                        | 79  |

|   |                                                          | 3.5.1                                                                     | Derivation of the Analytical Model                                   | 80  |

|   |                                                          | 3.5.2                                                                     | Modeling of traps effects                                            | 82  |

|   |                                                          | 3.5.3                                                                     | Results                                                              | 84  |

|   |                                                          | 3.5.4                                                                     | Conclusions                                                          | 88  |

| R | eferen                                                   | ices – C                                                                  | hapter 3                                                             | 90  |

| 4 | Role                                                     | of Car                                                                    | bon Doping in the Operation of Lateral GaN Power Devices             | 98  |

|   | 4.1                                                      | Wide-                                                                     | Band Gap Devices for New Generation Power Electronics                | 99  |

|   | 4.2                                                      | Backg                                                                     | round                                                                | 100 |

|   |                                                          | 4.2.1                                                                     | WBGs vs Si: Power Electronic Devices Metrics                         | 100 |

|   |                                                          | 4.2.2                                                                     | Elements of Physics of AlGaN/GaN HEMTs                               | 101 |

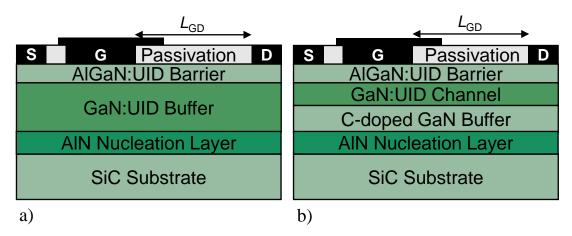

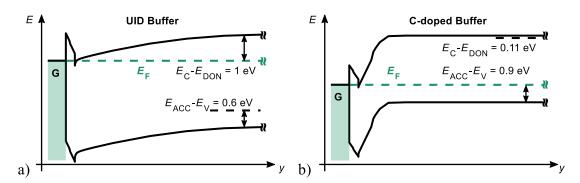

|   |                                                          | 4.2.3                                                                     | Architectures of GaN Lateral Devices                                 | 103 |

|   |                                                          | 4.2.4                                                                     | Breakdown Capability and Buffer Doping                               | 104 |

|   |                                                          | 4.2.5                                                                     | Trapping Mechanisms and Relative Detrimental Effects                 | 105 |

|   | 4.3                                                      | 3 Contribution: Mechanisms Underlying Three-Terminal Breakdown in Carbo   |                                                                      |     |

|   |                                                          | Doped                                                                     | GaN Power HEMTs                                                      | 110 |

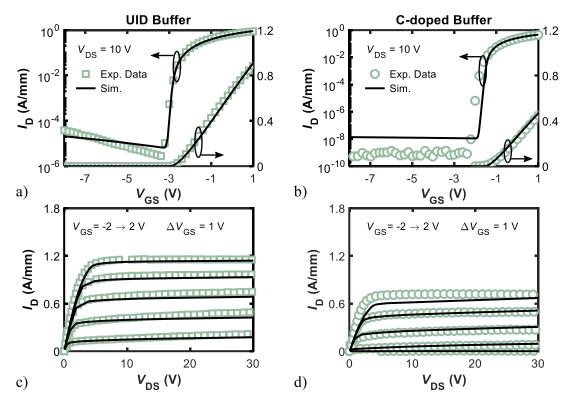

|   |                                                          | 4.3.1                                                                     | TCAD Simulation Setup                                                | 111 |

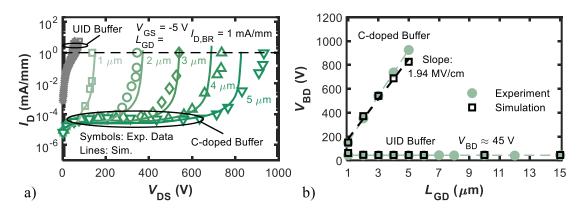

|   |                                                          | 4.3.2                                                                     | Breakdown Analysis                                                   | 113 |

|   |                                                          | 4.3.3                                                                     | Conclusions                                                          | 116 |

|   | 4.4                                                      | 4.4 Contribution: Influence of Buffer Traps on Dynamic ON- Resistance and |                                                                      |     |

|   | old Voltage Instabilities in C-doped GaN Power MIS-HEMTs |                                                                           | ltage Instabilities in C-doped GaN Power MIS-HEMTs                   | 117 |

|   |                                                          | 4.4.1                                                                     | Hole Redistribution To Explain ON-Resistance Stress/Recovery Experi- |     |

|   |                                                          |                                                                           | ments in AlGaN/GaN MIS-HEMTs                                         | 117 |

|   |                                                          | 4.4.2                                                                     | Bidirectional Threshold Voltage Instability After Negative Gate Bias |     |

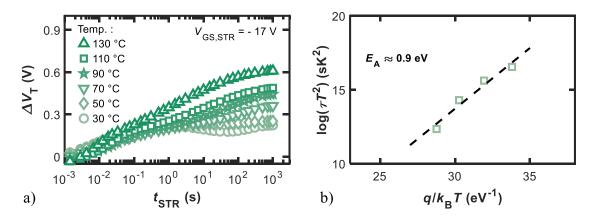

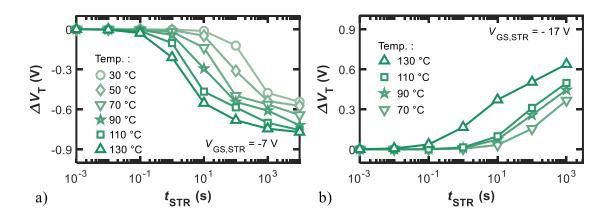

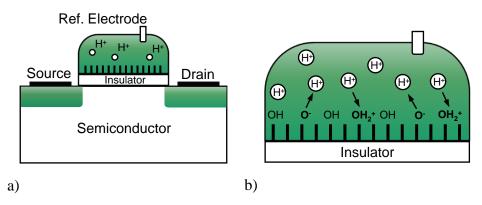

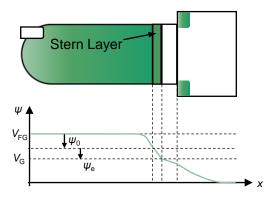

|   |                                                          |                                                                           | Stress in Carbon-doped Fully Recessed AlGaN/GaN MIS-HEMTs            | 124 |

|   |                                                          | 443                                                                       | Conclusions                                                          | 129 |

| Re | References – Chapter 4                                                                                    |                                                                          |                                                    | 131 |

|----|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------|-----|

| 5  | Negative Capacitance Effect to Beat Sensitivity Limits of Nano-Biosensors                                 |                                                                          |                                                    |     |

|    | 5.1                                                                                                       | Biosen                                                                   | sors and Nano-biosensors                           | 142 |

|    | 5.2                                                                                                       | Background                                                               |                                                    | 143 |

|    |                                                                                                           | 5.2.1                                                                    | Screening-limited response of FET-based Biosensors | 143 |

|    |                                                                                                           | 5.2.2                                                                    | Voltage Amplification with Negative Capacitance    | 152 |

|    | 5.3                                                                                                       | bution: Exploiting NCFETs to Beat Nernst Sensitivity Limit of Biosensors |                                                    |     |

|    |                                                                                                           | and Improving Signal-To-Noise Ratio                                      |                                                    | 158 |

|    |                                                                                                           | 5.3.1                                                                    | NC-BioFET Compact Model                            | 159 |

|    |                                                                                                           | 5.3.2                                                                    | Sensitivity Improvement                            | 163 |

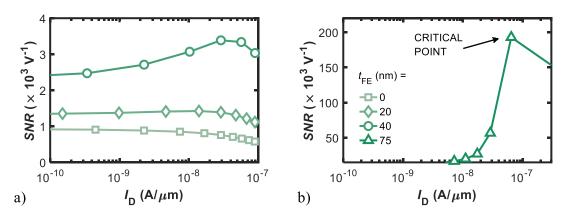

|    |                                                                                                           | 5.3.3                                                                    | Noise Rejection and SNR Improvement                | 165 |

|    |                                                                                                           | 5.3.4                                                                    | Conclusions                                        | 169 |

| Re | 5.3.1NC-BioFET Compact Model1595.3.2Sensitivity Improvement1635.3.3Noise Rejection and SNR Improvement165 |                                                                          |                                                    |     |

| 6  | Con                                                                                                       | clusions                                                                 | s and Outlook                                      | 175 |

| Li | st of I                                                                                                   | Publicat                                                                 | ions                                               | 177 |

# Acronyms

$\mathbf{k} \cdot \mathbf{p} \ \mathbf{k} \cdot \mathbf{p}$  Method

C-V Capacitance-Voltage Characteristics

I-V Current-Voltage Characteristics

P-E Polarization-Electric Field Relationship

**2DEG** Two-Dimensional Electron Gas

AI Artificial Intelligence

**BE** Bottom Electrode

**BGF** Band Gap Fluctuation

**BGOS** Back-Gating OFF-State Stress

**BioFET** FET-based (nano-) biosensor

**BLER** Body Line Edge Roughness

BT Border Trap

BTE Boltzmann Transport Equation

**BTO** Barium Titanate

**CB** Conduction Band

**CF** Conductive Filament

CMOS Complementary Metal-Oxide-Semiconductor

CVD Chemical Vapor Deposition

**DAE** Differential Algebraic Equation

**DD** Drift-Diffusion

**DFT** Density Functional Theory

**DG-UTB** Dual-Gate Ultra-Thin-Body

**DOS** Density of States

**DRAM** Dynamic Random Access Memory

**DUT** Device-Under-Test

FeFET Ferroelectric FET

FeRAM Ferroelectric Random Access Memory

FET Field-Effect Transistor

**FGOS** Front-Gating OFF-State Stress

FinFET Tri-Gate FET

FOM Figure-Of-Merit

GAA Gate-All-Around

GaAs Gallium Arsenide

GCA Gradual Channel Approximation

**GLER** Gate Line Edge Roughness

**HD** Hydro-Dynamic

**HEMT** High Electron-Mobility Transistor

HRS High-Resistance State

InAs Indium Arsenide

InGaAs Indium Gallium Arsenide

**InP** Indium Phosphide

IRDS International Roadmap for Devices and Systems

**ISFET** Ion-Sensitive FET

IT Interface Trap

ITF Interface Traps Fluctuation

ITRS International Technology Roadmap for Semiconductors

KCL Kirchhoff's Current Law

KVL Kirchhoff's Voltage Law

LER Line Edge Roughness

**LIM** Logic-In-Memory

LKE Landau-Khalatnikov Equation

LRS Low-Resistance State

LT Landau Theory

MC Monte Carlo

MFIS Metal-Ferroelectric-Insulator-Semiconductor

MFMIS Metal-Ferroelectric-Metal-Insulator-Semiconductor

MFS Metal-Ferroelectric-Semiconductor

MGG Metal Gate Granularity

MIM Metal-Insulator-Metal

MIS-HEMT Metal-Insulator-Semiconductor HEMT

MLDA Modified Local Density Approximation

MNA Modified Nodal Analysis

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MOVPE Metal Organic Vapor Phase Epitaxy

MSMC Multi Subband Monte Carlo

**NBTI** Negative Bias Temperature Instability

NC Negative Capacitance

NC-BioFET NC-BioFET

NC-BioFET Negative Capacitance FET-based biosensor

**NCFET** Negative Capacitance FET

**NEGF** Nonequilibrium Green's Function

NP-EMA Nonparabolic Effective Mass Approximation

**NVM** Non-Volatile Memory

**NW** Nanowire

OTF On-the-Fly

PCRAM Phase-Change Random Access Memory

**PUF** Physical Unclonable Function

PZT Lead Zirconium Titanate

QA Quantum Approach

QDD Quantum Drift-Diffusion

QHD Quantum Hydro-Dynamic

**RDD** Random Discrete Dopants

**RDF** Random Dopant Fluctuation

RNG Random Number Generator

**RRAM** Resistive Random Access Memory

RTN Random Telegraph Noise

**SBT** Strontium Bismuth Tantalate

S-IFM Statistical Impedance Field Method

SCA Semi-Classical Approach

**SDT** Source-Drain Tunneling

SIMS Secondary Ion Mass Spectroscopy

**SNR** Signal-to-Noise Ratio

SPE Suraface Potential Equation

SR Surface Roughness

**SRAM** Static Random Access Memory

**SRH** Shockley-Read-Hall

SRS Surface Roughness Scattering

STT-MRAM Spin-Transfer Torque Magnetic Random Access Memory

**TAT** Trap-Assisted Tunneling

TB Tight Binding

TCAD Technology Computer-Aided-Design

**TE** Top Electrode

**TEM** Transmission Electron Microscopy

TMD Transition Metal Dichalcogenide

**UID** Unintentionally Doped

VB Valence Band

WBG Wide Band Gap Semiconductor

WFF Work Function Fluctuation

WFP Wave-Function Penetration

# **List of Symbols**

$k_B$  Boltzmann Constant  $(8.671 \times 10^{-5} \, \text{eV/K})$

```

q Unit of Charge (1.602 \times 10^{-19} \, \mathrm{C})

\hbar Reduced Planck Constant (1.054 \times 10^{-34} \, \mathrm{J s})

\varepsilon_0 Vacuum Permittivity (8.854 \times 10^{-12} \, \mathrm{F/m})

V_{th} Thermal Voltage (25.85 \, \mathrm{mV}, \, \mathrm{at} \, T = 300 \, \mathrm{K})

E_F Fermi Energy (eV)

E_i Intrinsic Fermi Energy (eV)

E_{F,n} Electron Quasi-Fermi Energy (eV)

E_{F,p} Hole Quasi-Fermi Energy (eV)

J_{n,p} Electron (Hole) Current Density (\mathrm{A/m^2})

G_{n,p} Electron (Hole) Generation Rate (\mathrm{cm}^{-3} \, \mathrm{s}^{-1})

```

$R_{n,p}$  Electron (Hole) Recombination Rate (cm<sup>-3</sup> s<sup>-1</sup>)

$N_D$ ,  $N_A$  Donor (Acceptor) Impurity Density (cm<sup>-3</sup>)

n, p Free-Electron (Hole) Density (cm $^{-3}$ )

$n_i$  Intrinsic Carrier Density (cm<sup>-3</sup>)

- **E** Electric Field (V/m)

- $\rho$  Space-Charge Density (cm<sup>-3</sup>)

- $\varepsilon_s$  Semiconductor Dielectric Constant (F/m)

- $\kappa_s$  Semiconductor Relative Dielectric Constant (1)

- $\mu_n$ ,  $\mu_p$  Electron (Hole) Mobility (cm<sup>2</sup>/Vs)

- $D_n, D_p$  Electron (Hole) Diffusion Coefficient (cm<sup>2</sup>/s)

- Ψ Electrostatic Potential (V)

- $D_{IT}$  Interface Trap Density of States (eV<sup>-1</sup> cm<sup>-2</sup>)

- *I*<sub>D</sub> Drain Current (A/metre)

- $V_{DD}$  Supply Voltage (V)

- *I<sub>ON</sub>* ON-State Current (A/metre)

- *I<sub>OFF</sub>* OFF-State Current (A/metre)

- E<sub>C</sub> Conduction Band Minimum (eV)

- $E_V$  Valence Band Maximum (eV)

- $E_g$  Band Gap (eV)

- $m_n^*$  Effective Electron Mass (kg)

- $v_{inj}$  Injection Velocity (m/s)

- $C_G$  Gate Capacitance (F/m<sup>2</sup>)

- $C_{ox}$  Gate Oxide Capacitance (F/m<sup>2</sup>)

- $C_{inv}$  Inversion Layer Capacitance (F/m<sup>2</sup>)

- $C_S$  Semiconductor Capacitance (F/m<sup>2</sup>)

```

V_t Threshold Voltage (V)

```

SS Sub-threshold Slope (mV/dec)

$\vec{k}$  Wave Vector (m<sup>-1</sup>)

$\alpha_p$  Nonparabolocity Factor (eV<sup>-1</sup>)

$W_G$  Gate Width (m)

$L_G$  Gate Length (m)

$V_{GS}$  Gate to Source Voltage (V)

$V_{DS}$  Drain to Source Voltage (V)

$Q_n$  Mobile Electron Charge (C/cm<sup>2</sup>)

tox Gate Oxide Thickness (m)

EOT Equivalent Oxide Thickness (m)

t<sub>ch</sub> Channel Thickness (m)

$\mu(V_t)$  Threshold Voltage Average Value (V)

$\sigma(V_t)$  Threshold Voltage Standard Deviation (Variability) (V)

$\sigma_{TOT}(V_t)$  Total Threshold Voltage Variability (V)

$N_{SD}$  Source/Drain Doping (cm<sup>-3</sup>)

$\Delta_{rms}$  RMS Amplitude of LER-induced Variations (nm)

$\Lambda_{LER}$  Correlation Length of LER-induced Variations (nm)

x In Mole Fraction (In<sub>x</sub>Ga<sub>1-x</sub>As)

$N_{trap}$  Trapped Charge Density (cm<sup>-2</sup>)

$N_{inv}$  Inversion Charge Density (cm<sup>-2</sup>)

- t<sub>CF</sub> Conductive Filament thickness (m)

- $r_{CF}$  Conductive Filament radius (m)

- S<sub>CF</sub> Conductive Filament area (m<sup>2</sup>)

- $\rho_{CF}$  Restivity of Conductive Filament ( $\Omega$ m)

- $R_{CF}$  Restance of Conductive Filament ( $\Omega$ )

- t<sub>B</sub> Barrier thickness (m)

- $R_B$  Barrier resistance ( $\Omega$ )

- $T_B$  Barrier temperature (K)

- *I<sub>C</sub>* Current Compliance (A)

- $R_{LRS}$  LRS Resistance ( $\Omega$ )

- $V_{RESET}$  Reset Voltage (V)

- $V_{READ}$  Read Voltage (V)

- $P_s$  Saturation Polarization (C/cm<sup>2</sup>)

- $P_r$  Remnant Polarization (C/cm<sup>2</sup>)

- $E_C$  Coercive Field (V/m)

- $\alpha$  Landau 1<sup>st</sup>-Order Parameter (m/F)

- $\beta$  Landau 3<sup>rd</sup>-Order Parameter (m<sup>5</sup>/FC<sup>2</sup>)

- γ Landau 5<sup>th</sup>-Order Parameter (m<sup>9</sup>/FC<sup>4</sup>)

- $\rho$  Landau Damping Parameter ( $\Omega$ m)

- $\varepsilon_{FE}$  Ferroelectric dielectric constant (F/cm)

- $V_{FE}$  Ferroelectric potential (V)

$t_{FE}$  Ferroelectric layer thickness (m)

$C_{FE}$  Ferroelectric layer capacitance (F/cm<sup>2</sup>)

$N_A$  Acceptor doping concentration (cm<sup>-3</sup>)

$\mu_{eff}$  Effective Electron Mobility (cm<sup>2</sup>/Vs)

V<sub>ins</sub> Insulator Voltage (V)

$Q_{sw}$  Switching Charge ( $\mu$ C/cm<sup>2</sup>)

$V_{sw}$  Switching Voltage (V)

$V_{t,on}$  On-Threshold Voltage (V)

$V_{t,off}$  Off-Threshold Voltage (V)

MW Memory Window (V)

$|V_{P/E}|$  Program/Erase Pulse Amplitude (V)

$t_{P/E}$  Program/Erase Pulse Duration (s)

$\eta$  Power Conversion Efficiency

$R_{ON}$  ON-Resistance ( $\Omega$  mm)

V<sub>BD</sub> Breakdown Voltage (V)

$E_{crit}$  Critical Electric Field Strength for Avalanche Breakdown (V/m)

$\Phi_B$  Schottky Barrier Height (V)

$Q_{\pi}^{net}$  Net Polarization Charge at AlGaN/GaN interface (C/m<sup>2</sup>)

$\varepsilon_{AlGaN}$  Relative AlGaN Dielectric Constant

tbar AlGaN Barrier Thickness (m)

t<sub>2DEG</sub> 2DEG Centroid Distance From Interface (m)

$n_s$  2DEG Electron Density (cm<sup>-3</sup>)

$L_{GD}$  Gate-to-Drain Spacing (m)

$E_A$  Activation Energy (eV)

V<sub>SUB</sub> Substrate Voltage (V)

$\psi_s$  Surface Potential (V)

$Q_s$  Semiconductor Charge Density (C/cm<sup>2</sup>)

$Q_{surf}$  Surface Charge Density (C/cm<sup>2</sup>)

$Q_{dl}$  Double-Layer Charge Density (C/cm<sup>2</sup>)

$\psi_0$  Double-Layer Potential (V)

$\psi_e$  Stern Layer Potential (V)

$\beta_s$  Surface Buffer Capacity (cm<sup>2</sup>)

PSD Power Spectral Density (V<sup>2</sup>/Hz or A<sup>2</sup>/Hz)

$V_{INT}$  Internal gate potential (V)

V<sub>FB</sub> Flat-band Voltage (V)

A<sub>V</sub> Voltage gain

$Q_{MOS}$  MOSFET charge (C/cm<sup>2</sup>)

$C_{MOS}$  MOSFET capacitance (F/cm<sup>2</sup>)

$Q_{BIO}$  Biomolecules Charge Density (C/cm<sup>2</sup>)

$\lambda_{2D}$  Natural Length of the Device (nm)

$N_{2D}$  2D Effective Density of States (eV<sup>-1</sup> cm<sup>-2</sup>)

$N_d$  Net Impurity Density (cm<sup>-2</sup>)

$N_{BIO}$  Biomolecules Concentration (cm<sup>-2</sup>)

S<sub>I</sub> Current Sensitivity

## Chapter 1

## Introduction

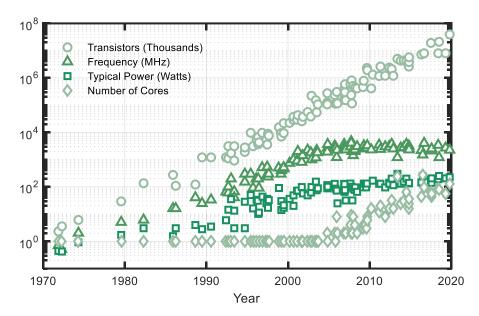

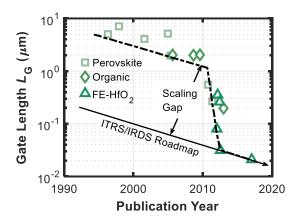

A common inside joke in the semiconductors community goes roughly as this: "the number of people predicting the demise of Moore's law doubles every two years". Behind the irony, there is a certain amount of truth regarding the ever-increasing challenges in keeping up with the strict demands of the original Moore's law. Since the early days of the semiconductor industry, Moore's law empirically predicted the doubling of transistors count on a chip every two years. The issues related to keeping up with Moore's law by relying on the traditional scaling rules defined by Dennard and co-workers in 1974 [1] became evident already at the end of the previous century, with International Technology Roadmap for Semiconductors (ITRS) forecasting a major roadblock already in 2005. Nonetheless, the number of transistors in a chip kept growing, see Fig. 1.1, and the semiconductor industry reached an outstanding global revenue of \$481 billion in 2018 [2], [3].

How was it then possible for the industry to keep growing despite predictions forecast a totally different scenario? Simply put, engineers and researchers were able to devise new strategies to continue scaling the Complementary Metal-Oxide-Semiconductor (CMOS) technology (i.e., the most widespread technology in integrated circuits) and circumvent the issues encountered with Dennard's scaling rules. This is certified by the Deloitte 2019 report that states: "The global semiconductor industry is set to continue its robust growth well into the next decade due to emerging technologies such as autonomous driving, artificial intelligence (AI), 5G and Internet of Things [...]" [3]. The plethora of new applications for the electronic devices stems from the

Figure 1.1: Performance indicators vs year of several commercial microprocessor from the early seventies up to year 2019. Circles: thousands of transistors per processor; triangles: operating frequency; squares: power consumption; diamonds: number of logical cores. After [4].

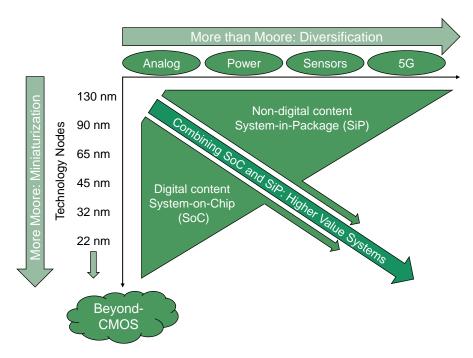

sparkling of novel technologies enabled by the developments in different research fields ranging from physics and semiconductor materials, to processing techniques and computing architectures. Correspondingly, a new international roadmap called International Roadmap for Devices and Systems (IRDS) was established in 2016, reflecting the shift to a top-down, application-oriented development paradigm. As illustrated in Fig. 1.2, IRDS bases its predictions and future directions on a scenario where heterogeneous integration of different functionalities on a single chip will enable the scaling of the technology to achieve even higher efficiency, speed, reliability (at the technology level) and augment the range of functions such as sensing, energy harvesting, energy conversion, analog computing (at the application level). Summarizing, the era of 21st-Century Electronics will be characterized by a plethora of novel technologies that will pair up with (or replace) Silicon-based transistors depending on the requirements of Automotive, Internet of Things, Machine Learning, Computing, Wireless (5G) Communications and many other applications.

In this hectic context, it is vital for technology manufacturers to be able to predict performance and reliability limits of novel solutions in order to speed up the time-to-market and increasing

Figure 1.2: More Moore (MM) and More than Moore (MtM) scaling if combined together provide both dimensional and functional scaling that are essential for the continuing development of semiconductor industry. Beyond-CMOS includes non-traditional devices for continuing dimension scaling. Adapted from [5].

process yield. These goals can only be met by recurring to simulation and modeling tools that allow gaining insights into device behavior and observing phenomena that could not be measured on real devices (due to issues related to production costs and timelines) [6]. Mimicking devices (or circuits) behavior with simulations to reproduce experimental results has actually been common practice since the late 1970's. However, with the recent emergence of novel technologies either at the nanometre scale, of different semiconductor materials, as well as of different physical principles to encode information (e.g., spin-based devices), simulations have become fundamental for understanding – and thus engineering – these technologies. Goal of well-calibrated simulation models is to reproduce (and predict) device behavior under different conditions (that can be for instance geometrical parameter variations, bias, temperature, etc.) in a relatively short time compared to real experiments. One of the main concerns of the device physicist/engineer is the trade-off between accuracy and simulation time. Thus, any good simulation set-up should strive to be as comprehensive as possible to consistently reproduce and predict measurement results in

the least (computational) time possible.

In this thesis, state-of-the-art simulation and compact modeling tools are exploited to analyze the performance and reliability limits of several different emerging technologies. Specifically, in this dissertation we address four application scenarios and the corresponding candidate technologies to provide enhanced performance compared to Si-based counterparts. These are: *i)* III-V Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) for logic/digital circuits, *ii)* Resistive Random Access Memories (RRAMs) and Ferroelectric FETs (FeFETs) for non-volatile memory and in-memory computing, *iii)* GaN-based High Electron-Mobility Transistors (HEMTs) for power applications, and *iv)* Negative Capacitance FETs (NCFETs) for biosensing. In the context of Fig. 1.2, III-V MOSFETs belong to the 'More Moore' chapter of the IRDS roadmap, RRAMs and FeFETs belong to the 'Beyond CMOS' chapter [7], GaN HEMTs to the 'More than Moore', and Negative Capacitance FET-based biosensors (NC-BioFETs) make use of a 'Beyond CMOS' technology (i.e., NCFETs) to improve a 'More than Moore' device such as the nano-biosensor.

In the remainder of this chapter we briefly introduce some general concepts about the simulation paradigms that are at the basis of any theoretical analysis concerning semiconductor devices. Then, we will discuss process and device simulations that are used to understand in detail the fabrication processes and physical mechanisms influencing the single device operation. Finally, we discuss SPICE simulations that are employed to evaluate the single (or multiple) device behavior in the context of circuit applications.

## 1.1 Semiconductor Device Simulation and Modeling

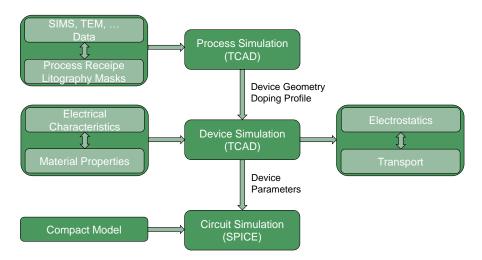

Due to the complexity of device's geometry and the amount of physical processes involved, semiconductor device simulations are carried out at three different levels of abstraction [8]. This allows to effectively understand the influence of single processing steps or physical models in the general behavior of the device. This differentiation gives rise to a hierarchy of abstraction levels in which the devices are considered. The schematic of the general hierarchy of semiconductor device simulation is depicted in Fig. 1.3. The first tier is represented by the so-called process simulations

Figure 1.3: General Hierarchy of Semiconductor Device Simulation.

that aims at virtually reproducing the fabrication steps performed in the white-room to realize a semiconductor device. The second tier is represented by the actual device simulations that aim at reproducing (and predicting) with physical models the electrical behavior of a device. The final tier is constituted by the circuit simulations that use device models to produce complex functions at circuit level (i.e., with many devices connected together). In the following we describe more in detail each of the hierarchy tiers.

#### 1.1.1 Process Simulation

The models implemented in the process simulation tier range from the epitaxial growth of semiconductor layers to implantation and diffusion of doping atoms in the semiconductor regions to oxidation, etching and lithography. The simulation models used to reproduce device processes are normally included in softwares of Technology Computer-Aided-Design (TCAD) suites such the commercial Sentaurus Process (Synopsys, Inc.), and Victory Process (Silvaco, Inc.) as well as other open-sources alternatives. The inputs required by process simulation are the doping profiles as obtained from Secondary Ion Mass Spectroscopy (SIMS) measurements, topography provided by Transmission Electron Microscopy (TEM), the process recipe, and the lithography masks, see Fig. 1.3. These inputs are necessary in order to reproduce accurately the actual fabricated device geometry and doping profiles. The recreated device geometry and doping profiles are then used

Figure 1.4: Schematic of the Device Simulation Sequence. Adapted from [6].

as input for the proper device simulations, described in the following section<sup>1</sup>.

#### 1.1.2 Device Simulation

After the device geometry and doping profiles have been generated by the process simulation, the device (physics) simulation can take place. As for the previous tier, device simulations are carried out by TCAD tools (e.g., the commercial Sentaurus Device and Victory Device) that include several physical models to compute the electromagnetic fields and the charges flowing inside of a device to determine its electrical behavior. To perform these simulations, the device is sub-divided into a discretized structure called *mesh*. Thus each differential equation of the system defining the device behavior is solved at each of the mesh vertices. Clearly, both accuracy and speed of the simulation heavily depend on the definition of the mesh: a fine mesh leads to more accurate results than a coarse one but at the cost of higher computational time.

As for the process simulation, device simulation requires input files obtained from the measurements of electrical characteristics (e.g., Current-Voltage Characteristics (I-V) and Capacitance-Voltage Characteristics (C-V)) and material properties obtained from either measurements or by sophisticated calculations performed at the microscopic level (e.g., Density

<sup>&</sup>lt;sup>1</sup>We mentioned process simulations for the sake of completeness. In fact, for the rest of this thesis we will not make further use of them, rather we will use tools that allow defining both geometry and doping in a simplified manner than can be used as input to device simulations.

Figure 1.5: Hierarchy of Transport Models.

Functional Theory (DFT) simulations to determine the band-structure, Monte Carlo (MC) simulations to obtain the carriers' mobility profiles, etc.). This data is necessary in order to *calibrate* the results obtained by the simulations with the real device characteristics. The calibration not only guarantees that simulations represent the actual device behavior but also that they can be used to predict behavior when for instance device parameters are varied.

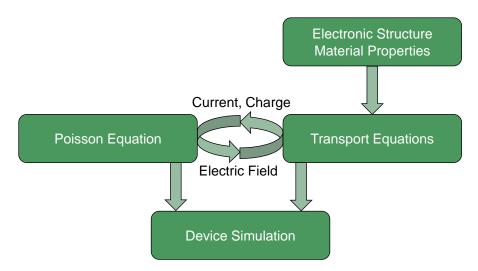

The schematic representation of the device simulation sequence is depicted in Fig. 1.4. Basically, a device simulation run computes the solution of the coupled electrostatic and transport equations. The electrostatics is generally determined by the Poisson equation [6] and allows to determine the electric field distribution across all regions and layers of a device. The field is used to determine the current and charge in the device from the carrier density profiles determined by the transport equations. The charge computed via the transport equations is fed-back to the Poisson equation and the final solution is found by a self-consistent iterative procedure. In this scheme, a list of parameters describing the electronic structure and material properties needs to be provided for each of the different layers constituting the device geometry to obtain meaningful results.

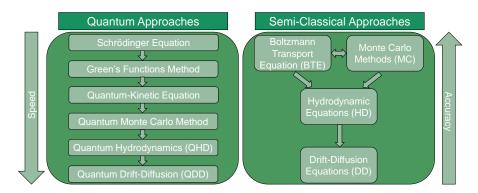

While the electrostatic problem is essentially determined by the solution of the Poisson equation, the transport problem can be approached at different levels of accuracy depending on the complexity of the geometry and on the dimension scale of the device [6]. The transport models are generally categorized depending on whether they are based on semi-classical or quantum approaches, as shown in Fig. 1.5.

#### **Semi-Classical Approaches**

The Semi-Classical Approaches (SCAs) treat electronic charges as particles and make use of either approximations of the Boltzmann Transport Equation (BTE) or solve exactly the problem by using MC methods to determine (statistically) the dynamics and scattering of each particle involved into the device behavior [9]<sup>2</sup>. However, due to the complexity and computational burden of MC methods, BTE is generally approximated by using the so-called moment's method that creates a set of balance equations derived from the BTE itself by performing appropriate integrals and averages over the momentum space [9]<sup>3</sup>. The models approximating the BTE that are mostly used are the Hydro-Dynamic (HD) and Drift-Diffusion (DD) equations.

#### **Quantum Approaches**

When the device dimensions scale down to the nanometer level, carrier transport behaves quite differently than how would SCAs predict. This is because the carriers' wave nature giving rise to phenomena like tunneling and limited (or absence of) scattering in their traveling range leads to more complex behavior. This is where Quantum Approaches (QAs) come into play. Fig. 1.5 summarizes the transport models based on QAs. The most general and also complex QA is based on the direct solution of the Schrödinger equation, to determine the wave function for each carrier involved in the device operation. This approach however is rather impractical unless for simplified problems where few carriers are considered. At the other end of the spectrum, there exist the Quantum Hydro-Dynamic (QHD) and Quantum Drift-Diffusion (QDD) equations that are the quantum equivalent of the relative SCA. These equations resemble basically the SCA ones,

$$f(E) = \frac{1}{1 + \exp\left[\frac{(E - E_F)}{k_B T}\right]} \tag{1.1}$$

(where E is the energy of the carrier, and T the lattice temperature) is in fact only valid for near-equilibrium transport, which is often not the case [9].

<sup>&</sup>lt;sup>2</sup>It is worth mentioning that much progress has been made in the last 10-15 years in developing the deterministic methods to solve the BTE for low dimensional systems, see for instance [10], [11] and [12] for deterministic solutions of the BTE for a 1D electron gas (e.g. Nanowire (NW) transistors) and for 2D systems, respectively.

<sup>&</sup>lt;sup>3</sup>The main issue when approximating the BTE is the necessity to make an *a priori* assumption on the carrier distribution function, which is not required by MC methods. For instance, the well-known Fermi distribution function

including correction in the carrier density profile to take into account quantum confinement<sup>4</sup>. More details regarding each of these approaches can be found in [6].

#### 1.1.3 Drift-Diffusion Equations

We now describe the general equations of the DD model as they constitute the simplest treatment of semiconductor device behavior. The DD model of transport is the most simplified view of how actually a device works. Nevertheless, this paradigm was employed for a long time in simulations (and still is) thanks to its simplicity and ease of implementation in numerical solvers, constituting the starting point of the understanding of most semiconductor devices. The DD equations describe the carriers motion in a semiconductor crystal with applied external electric field as a combination of acceleration and scattering events through the paths of the carriers that determine the current flows [13]. The DD equations are also known as the Semiconductor Equations and are summarized as follows (for both electrons and holes)

$$\frac{\partial n}{\partial t} = -\nabla \cdot \left(\frac{\mathbf{J}_n}{q}\right) + G_n - R_n \tag{1.2a}$$

$$\frac{\partial p}{\partial t} = -\nabla \cdot \left(\frac{\mathbf{J}_p}{q}\right) + G_p - R_p \tag{1.2b}$$

$$\nabla \cdot (\varepsilon_{s} \mathbf{E}) = \rho. \tag{1.2c}$$

Eqs. (1.2a) and (1.2b) are the *continuity* equations for electrons and holes, respectively. They basically express a balance equations for electron (hole) density over time, taking into account the in/out flux (expressed by the current  $J_{n,p}$ ) and the generation/recombination rates (expressed by  $G_{n,p}$  and  $R_{n,p}$ , respectively). Eq. (1.2c) is the local-form of Maxwell's equation resembling the Poisson equation in space. To solve Eqs. (1.2a) to (1.2c) one needs to write three additional equations to determine  $J_{n,p}$  and E.

The electron and hole current densities  $(J_{n,p})$  are determined by the so-called *current* equa-

<sup>&</sup>lt;sup>4</sup>This aspect will be discussed more in detail when analyzing the behavior of ultra-scaled III-V MOSFETs in Chapter 2.

tions, that read

$$\boldsymbol{J}_n = q\boldsymbol{\mu}_n n\boldsymbol{E} + qD_n \nabla n \tag{1.3a}$$

$$\boldsymbol{J}_{p} = q\mu_{p}p\boldsymbol{E} - qD_{p}\nabla p. \tag{1.3b}$$

Both mobility and diffusion coefficient depend on electric field in general; however, under non-degenerate conditions (i.e., the Fermi level is *inside* the band-gap) Einstein relationship can be shown to hold true

$$D_{n,p} = \mu_{n,p} \left( \frac{k_B T}{q} \right) = \mu_{n,p} V_{th}. \tag{1.4}$$

The free carrier's densities at equilibrium can be simply determined by using Boltzmann approximation of Fermi-Dirac's statistics, obtaining [13]

$$n = n_i \exp\left[\frac{(E_F - E_i)}{k_B T}\right], \quad p = n_i \exp\left[\frac{(E_i - E_F)}{k_B T}\right]. \tag{1.5}$$

Under equilibrium condition,  $np = n_i^2$  ( $n_i = 1 \times 10^{10}$  cm<sup>-3</sup> for Silicon). Under non-equilibrium conditions, it is no longer possible to define a single Fermi energy for the whole semiconductor. It is thus useful to write *quasi* Fermi levels for electrons ( $E_{F,n}$ ) and holes ( $E_{F,p}$ ) so that the two pools of carriers result under equilibrium within themselves. Now we have

$$n = n_i \exp\left[\frac{(E_{F,n} - E_i)}{k_B T}\right] \tag{1.6a}$$

$$p = n_i \exp\left[\frac{(E_i - E_{F,p})}{k_B T}\right]$$

(1.6b)

$$np = n_i^2 \exp\left[\frac{(E_{F,n} - E_{F,p})}{k_B T}\right].$$

(1.6c)

Thus finally by using Eqs. (1.4), (1.6a) and (1.6b) to rewrite Eqs. (1.3a) and (1.3b) we obtain

$$\boldsymbol{J}_n = -\,\mu_n n \nabla E_{F,n} \tag{1.7a}$$

$$\boldsymbol{J}_{p} = -\mu_{p} p \nabla E_{F,p}. \tag{1.7b}$$

Eqs. (1.7a) and (1.7b) are the form of current equations commonly employed in simulators.

The electric field (E) is obtained through  $\rho$ , which can be solved for by applying the charge-neutrality condition in the bulk of the semiconductor

$$\rho = -q (n - p + N_A - N_D). \tag{1.8}$$

By substituting Eq. (1.8) in Eq. (1.2c), coupled self-consistently with Eqs. (1.7a) and (1.7b),  $\mathbf{E}$  can be determined and, consequently, the electrostatic potential ( $\psi$ ) in the device as  $\mathbf{E} = -\nabla \psi$ .

#### 1.1.4 Circuit Simulation and Compact Modeling

According to the scheme in Fig. 1.3, the last tier of semiconductor device modeling is represented by circuit simulation augmented by the use of compact models. Circuit simulations are most commonly carried out with a SPICE simulator, that constructs a mathematical model of the circuit comprising the device and the external components, the topological network of the circuit itself as well as the parasitic elements (resistors, capacitors, inductors) [14]. A circuit simulator basically constructs a system of coupled non-linear Differential Algebraic Equations (DAEs) of the form

$$\mathbf{F}(\mathbf{x}, \dot{\mathbf{x}}, t) = 0 \tag{1.9}$$

where x are the unknowns of the system. Based on the Modified Nodal Analysis (MNA), the system of Eq. (1.9) can be augmented to solve for the branch voltages and nodal currents for each element of the circuit including the external sources [14]. The problem is solved by employing iterative algorithms that allow to find the self-consistent solution of the system (if it exists). Note that a circuit simulator does not solve for Maxwell's equations but rather for Kirchhoff's Voltage Laws (KVLs) and Kirchhoff's Current Laws (KCLs), thus the wires are treated as ideal conductors and hence the external fields are assumed not to affect each element internal behavior. This in turn implies that each element must be charge neutral within itself [14].

Compact models represent the mathematical abstraction of complex device behavior, written commonly in Verilog-A [14] in such a way to be solved fast, accurately and robustly by the circuit simulator. Compact models are so widely employed that there exist industry-standard models that are employed by companies to mimic the behavior of their own products (e.g., BSIM,

PSP, EKV for transistors<sup>5</sup>). As for process and device simulations, compact models need to be calibrated in order to reproduce (and predict) accurately the behavior of real components. The calibration in this case is done by extracting the device parameters of interest from the output of device TCAD simulations. This way one guarantees that the compact model is able to reproduce a device behavior in a circuit application.

### 1.2 Outline

Having defined the simulation and modeling frameworks that will be used in this thesis, we now briefly summarize the content discussed in detail in the next chapters

- Chapter 2 discusses ultra-scaled III-V MOSFETs for future nodes of Moore's law. TCAD

simulations are employed to investigate the influence of traps in the mobility extraction

method and to study variability issues.

- 2. Chapter 3 treats the modeling of noise and endurance in RRAMs and FeFET, respectively.

- 3. Chapter 4 investigates the stability and reliability issues in GaN HEMTs for power applications. TCAD simulations are employed to reveal the role of Carbon doping in the buffer on breakdown voltage, on-resistance degradation and recovery transients and bidirectional threshold voltage shifts.

- 4. Chapter 5 presents the concept of a potentiometric nano-biosensor based on the 2D semiconductor MoS<sub>2</sub> exploiting the *negative capacitance* effect to improve sensitivity and Signal-to-Noise Ratio (SNR).

Finally, Chapter 6 draws the conclusions of this work and offers an outlook on the future of TCAD simulations augmented with Artificial Intelligence (AI) tools.

<sup>&</sup>lt;sup>5</sup>A more exhaustive list of transistor compact models is available at https://en.wikipedia.org/wiki/Transistor\_model#Popular\_models.

# **References – Chapter 1**

- [1] R. H. Dennard, F. H. Gaensslen, H. N. Yu, V. L. Rideout, E. Bassous, and A. R. Leblanc, "Design of Ion-Implanted MOSFET's With Very Small Physical Dimensions," *IEEE Journal of Solid-State Circuits*, vol. 9, no. 5, pp. 256–268, Oct. 1974. DOI: 10.1109/JSSC. 1974.1050511.

- [2] *Semiconductor industry Wikipedia*. [Online]. Available: https://en.wikipedia.org/wiki/ Semiconductor\_industry (visited on 10/14/2020).

- [3] Deloitte, "Semiconductors-the Next Wave Opportunities and winning strategies for semiconductor companies," Tech. Rep., 2019.

- [4] K. Rupp, 40 Years of Microprocessor Trend Data. [Online]. Available: https://www.karlrupp.net/2015/06/40-years-of-microprocessor-trend-data/ (visited on 11/13/2020).

- [5] IEEE, "International Roadmap for Devices and Systems (IRDS) 2020 More than Moore White Paper," Tech. Rep., 2020. [Online]. Available: https://irds.ieee.org/editions/2020/ more-than-moore.

- [6] D. Vasileska, S. M. Goodnick, and G. Klimeck, *Computational Electronics*, 1st ed. Boca Raton (FL, USA): CRC Press, 2010. DOI: 10.1201/b13776.

- [7] IEEE, "International Roadmap for Devices and Systems (IRDS) 2020 Beyond CMOS," 2020. [Online]. Available: https://irds.ieee.org/editions/2020/beyond-cmos.

- [8] A. Gehring, "Simulation of Tunneling in Semiconductor Devices," PhD Dissertation, TU Wien, 2003. [Online]. Available: https://www.iue.tuwien.ac.at/phd/gehring/diss.html.

- [9] D. Esseni, P. Palestri, and L. Selmi, *Nanoscale MOS Transistors*, 1st ed. Cambridge (UK): Cambridge University Press, 2011. DOI: 10.1017/CBO9780511973857.

- [10] M. Lenzi, P. Palestri, E. Gnani, S. Reggiani, A. Gnudi, D. Esseni, L. Selmi, and G. Baccarani, "Investigation of the transport properties of silicon nanowires using deterministic and Monte Carlo approaches to the solution of the Boltzmann transport equation," *IEEE Transactions on Electron Devices*, vol. 55, no. 8, pp. 2086–2096, 2008. DOI: 10.1109/TED.2008.926230.

- [11] O. Badami, E. Caruso, D. Lizzit, P. Osgnach, D. Esseni, P. Palestri, and L. Selmi, "An Improved Surface Roughness Scattering Model for Bulk, Thin-Body, and Quantum-Well MOSFETs," *IEEE Transactions on Electron Devices*, vol. 63, no. 6, pp. 2306–2312, 2016. DOI: 10.1109/TED.2016.2554613.

- [12] C. Jungemann, J. A. Pham, B. Meinerzhagen, C. Ringhofer, and M. Bollhöfer, "Stable discretization of the Boltzmann equation based on spherical harmonics, box integration, and a maximum entropy dissipation principle," *Journal of Applied Physics*, vol. 100, no. 2, 2006. DOI: 10.1063/1.2212207.

- [13] W. Fichtner, D. J. Rose, and R. E. Bank, "Semiconductor Device Simulation," *IEEE Transactions on Electron Devices*, vol. 30, no. 9, pp. 1018–1030, 1983. DOI: 10.1109/T-ED.1983.21256.

- [14] C. C. McAndrew, G. J. Coram, K. K. Gullapalli, J. R. Jones, L. W. Nagel, A. S. Roy, J. Roychowdhury, A. J. Scholten, G. D. J. Smit, X. Wang, and S. Yoshitomi, "Best Practices for Compact Modeling in Verilog-A," *IEEE Journal of the Electron Devices Society*, vol. 3, no. 5, pp. 383–396, Sep. 2015. DOI: 10.1109/JEDS.2015.2455342.

### Chapter 2

# Traps and Variability Issues in III-V MOSFETs

Abstract — In this chapter we investigate the issues related to traps and variability in III-V MOSFETs.

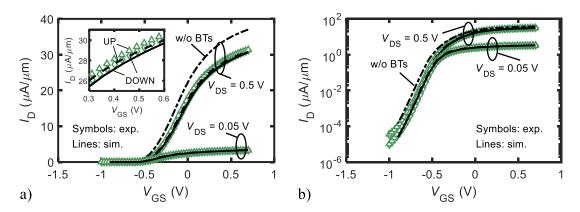

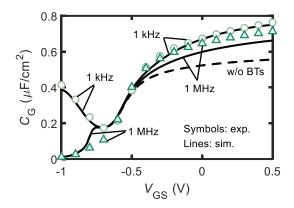

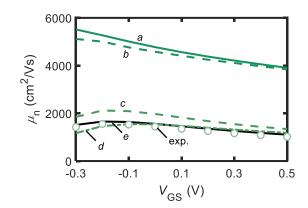

First, we perform a combined experimental/simulation analysis of InGaAs planar MOSFETs to evaluate the effects of Interface Traps (ITs) and Border Traps (BTs) on the electrical characteristic and on the accuracy of split-CV mobility measurements. We find that BTs induce hysteresis in the quasi-static I-V characteristics and lead to frequency dispersion in the C-V curves. Moreover, we find that traps affect mobility measurements due to the spurious contributions of trapped charge to the total gate charge.

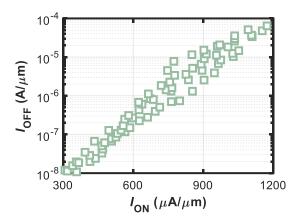

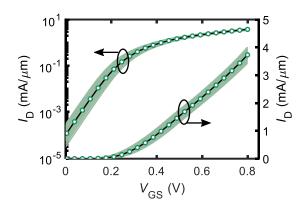

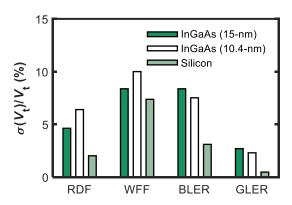

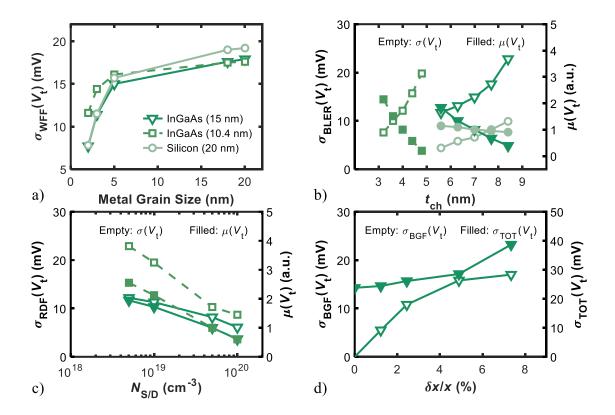

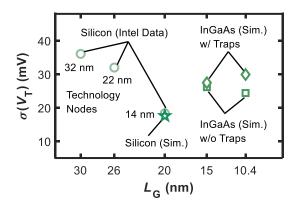

Second, we investigate the statistical variability of threshold voltage in InGaAs ultra-thin-body MOSFETs. InGaAs devices have comparatively higher variability than Si counterparts as a result of stronger quantization effects in the ultra-thin channel. The most relevant variability sources are the gate work function fluctuation and line edge roughness. Dimension scaling enhances  $V_t$  sensitivity to  $t_{ch}$  variations, configuring the control over  $t_{ch}$  as the most critical design issue. At extremely scaled nodes, the variability due to interface traps plays a significant role that could ultimately contrast the trend of reduced variations with smaller dimensions, as opposite to Si devices.

### 2.1 Scaling of Logic Transistors — III-Vs to the rescue

As mentioned in the Introduction, the strict requirements demanded by Moore's law to keep up with its predictions led to the exploration of novel technologies to extend the scaling of CMOS technology. One pathway in the quest towards enhanced performance at smaller dimensions was towards replacing the Si channel material with III-V compound semiconductors. III-V's offer enhanced mobility compared to Si leading to uncompromised performance when reducing supply voltage [1]. One of such III-V materials in Indium Gallium Arsenide (InGaAs), that has an outstanding bulk (electron) mobility of  $10\,000\,\mathrm{cm^2/Vs}$  against  $1400\,\mathrm{cm^2/Vs}$  of Si (i.e., about a factor of 10 improvement) [2]. Since the speed of an integrated CMOS chip is proportional to the output current  $I_D$  (for a given supply voltage,  $V_{DD}$ ) and, in turn, to the mobility  $\mu_n$  [4], then clearly a mobility boost would directly translate to speed enhancement. Although several ultra-scaled and high-speed III-V MOSFETs have already been experimentally demonstrated [5]-[7], these devices still suffer from parasitic effects that reduce their potential benefits over their Si counterparts [41], [48], [55]. In particular, these issues are relative to: i) the high density of defects in the gate oxide (i.e., BTs) and at the interface with the channel (i.e., ITs), ii) the statistical variability that causes identical devices to have different performance, iii) the low Density of States (DOS) reducing the maximum achievable electron density, and iv) the band-toband tunneling leading to high off-state leakage [8, Ch. 1]. These issues still need to be fully understood — and consequently reduced — through proper engineering solutions to fully exploit the superior, intrinsic channel material properties of InGaAs.

In this chapter we will present the research work on the detrimental role of ITs and BTs on the mobility and on the variability of III-V MOSFETs. The findings in this chapter were obtained by performing TCAD device simulations calibrated either on experimental results or on more sophisticated simulation models, as discussed later. Before discussing these results, we will provide some background knowledge by reviewing relevant prior work on this topic.

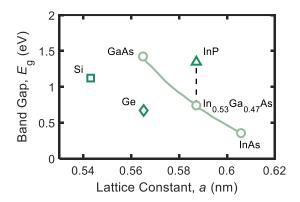

Figure 2.1: Energy bandgap  $E_g$  vs lattice constant a of different semiconductor materials, showing that  $In_{0.57}Ga_{0.43}As$  has the same lattice constant as InP. Adapted from [3].

### 2.2 Background

### 2.2.1 InGaAs Properties

As mentioned before, InGaAs is a compound material combining the properties of column III and V semiconductors to achieve high speed and low power consumption. Basically, InGaAs is a mixture of the binary compounds Indium Arsenide (InAs) and Gallium Arsenide (GaAs), where the molar fraction x of In with respect to Ga defines the electrical properties of the material. We focus on the In<sub>0.57</sub>Ga<sub>0.43</sub>As compound as this particular stoichiometry gives a semiconductor that is lattice-matched to Indium Phosphide (InP), as shown in Fig. 2.1, allowing to obtain high quality epitaxial layers with either no tensile or compressive strain [9], [10]. InGaAs has a bulk mobility of about  $10000 \,\mathrm{cm}^2/\mathrm{Vs}$  and a band-gap  $E_g$  of about  $0.74 \,\mathrm{eV}$ . Clearly the properties of InGaAs lay somewhere in between those of InAs and GaAs and represent a good compromise to guarantee both high  $I_{ON}$  (through mobility) and low  $I_{OFF}$  (through bangap) [4].

The high mobility of InGaAs can be attributed to the low effective mass of this material compared to that of Si. In the classical picture in fact, the velocity of an electron in a semiconductor crystal in presence of an external electric field can be simply determined as

$$v_n = \frac{p_n}{m_n^*} = -\frac{q\tau_n}{m_n^*} E_x = -\mu_n E_x \tag{2.1}$$

where  $v_n$  is the electron velocity,  $p_n = -q\tau_n E_x$  its momentum (with  $\tau_n$  being the mean time

between scattering and  $E_x$  the electric field component along the arbitrary 1D direction), and  $m_n^*$  is the electron effective mass. From this simple relationship it becomes clear that as  $m_n^*$  is reduced,  $\mu_n$  is increased<sup>1</sup>. The low effective mass of InGaAs ( $m_t = 0.041 \, \mathrm{m_0}$  [2]) compared to that of Si ( $m_t = 0.19 \, \mathrm{m_0}$ ) not only leads to a mobility improvement but also to a reduction of the available states in the Conduction Band (CB) (i.e., the so-called DOS bottleneck) [12] and in an increase of quantization effects [11]. Strong quantization and low DOS lead on the one hand to a reduction in electron available for conduction and hence reduced  $I_{ON}$ , and, on the other hand, to an increased probability of source-drain tunneling hand hence higher  $I_{OFF}$  [12]. Thus, design of InGaAs devices need to careful take into account the material properties in order to achieve higher performance compared to Si counterparts. Previous theoretical analysis considering the trade-offs between the aforementioned aspects concluded that III-V semiconductors could offer enhanced performance for CMOS applications only for low power operation [11].

### 2.2.2 Quantum Correction to Carrier Density in Ultra-Scaled Devices

In this section we briefly discuss how quantization effects can be accounted for in TCAD simulations to correctly model the electron density in the channel. In classical MOSFET theory, it is generally assumed that an infinitely small inversion layer is formed between the source and drain (i.e., the channel), leading to the conclusion that above threshold the gate capacitance  $C_G$  is equal to  $C_{ox}$  [13]. Actually, the inversion layer has a finite thickness because the electrons crowding near the interface with the insulator have a peak in their distribution (called centroid) which is physically distant from the interface, giving a finite inversion layer thickness and hence finite capacitance  $C_{inv}$ . As device dimensions reduce, the inversion layer thickness becomes important (because the relative ratio between  $C_{inv}$  and  $C_{ox}$  decreases) as  $C_G$  is defined as the series of  $C_{ox}$  and  $C_S$  (i.e., the semiconductor capacitance). In addition, it can be shown that  $C_S$  is directly related to the DOS of the semiconductor [4], thus for materials like InGaAs the  $C_G$  reduction due to quantum confinement is more prominent than for Si.

<sup>&</sup>lt;sup>1</sup>Generally, carrier transport for InGaAs devices (especially at nanometre scale) requires a more detailed treatment due to the limits of the classical theory and the appearance of quantum mechanical effects. Revision of the classical MOSFET theory led to the definition of a quantity called injection velocity  $v_{inj}$  upon which a direct relationship with  $I_{ON}$  can be established (rather than on mobility) [4]. Nonetheless, it can still be shown that  $v_{inj}$  inversely depends on  $m_n^*$ , keeping the argument about speed improvement with  $m_n^*$  reduction valid [4].

In order to evaluate correctly the carrier density in the channel (and  $C_G$  consequently) a quantum mechanical treatment is required. Taking into consideration the bandgap widening induced by the discreteness of the CB available levels (for electrons), the classical carrier density becomes

$$n = N_C \exp\left(\frac{E_{F,n} - E_C - \Lambda_n}{k_B T}\right) \tag{2.2}$$

where  $N_C$  is the conduction band effective density of states [13], and  $\Lambda_n$  is the first available energy level (i.e., the first subband) in the conduction band [4]. This approach is indeed the one followed by TCAD simulation softwares [14].

### 2.2.3 InGaAs MOSFET Architectures

Before discussing InGaAs MOSFET architectures, it is important to stress on their operation mode, which differs from classical Si MOSFETs. As mentioned previously in fact, in classical n-type MOSFETs the channel charge is composed of electrons that are the minority carriers in the semiconductor body region (p-type). This is why the channel layer is also called the *inversion* layer and the device 'inversion-type'. InGaAs MOSFETs on the other hand, are called *accumulation-type* because the body is normally undoped or lightly doped (to compensate for the native conductivity).

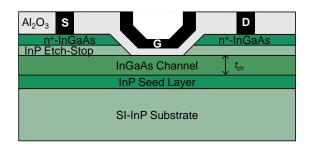

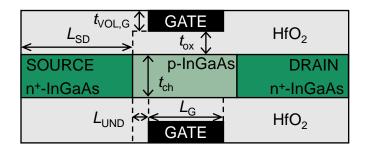

As for conventional Si-based MOSFETs, several device architectures were explored for InGaAs, ranging from planar [5], [18] to Dual-Gate Ultra-Thin-Bodys (DG-UTBs) [10], Tri-Gate FETs (FinFETs) [6], [7], [19], and Gate-All-Around (GAA) NWs [20], [21]. The cross-section of the planar MOSFET discussed in [18] (and used for the analysis in Section 2.3) is shown in Fig. 2.2. Depending on the particular device architecture, several critical aspects related to either quantum confinement or tunneling become more or less severe. This is true also for the effect of traps on the device electrostatic behavior and transport. In Section 2.3 and Section 2.4 we will present simulation results for the planar MOSFET and the DG-UTB architecture, respectively.

Figure 2.2: Sketch of the cross-section of the simulated InGaAs planar MOSFET.

### 2.2.4 Simulation Approaches

InGaAs is a direct bandgap material, meaning that the CB minimum and Valence Band (VB) maximum are aligned in the k-p space, thus making it an excellent material also for photonics applications (e.g. LEDs, lasers). Its band structure is quite different from that of Si [2] in the sense that it exhibits strong non-parabolicity in the vicinity of CB minimum (and VB maximum). Conventional TCAD simulators based on the DD equations and on the near-equilibrium transport<sup>2</sup> treat the band structure in a simplified manner such that it can be approximated as a (quasi-) parabolic function near its local minimum/maximum. Thus, the energy of carriers in the vicinity of the CB minimum can be simply written as

$$E(\vec{k})[1 + \alpha_p E(\vec{k})] = E_C + \frac{(\hbar \vec{k})^2}{2m_n^*}$$

(2.3)

where  $\alpha_p$  is the so-called nonparabolicity factor (for  $\alpha_p = 0$  we obtain a parabolic energy dispersion) that accounts for the deviation from parabolic shape when moving away from the CB minimum. InGaAs exhibits strong nonparabolicity that affects effective mass [23] as well as DOS calculation<sup>3</sup>. It is therefore of paramount importance to determine the band structure accurately and thus extract the material parameters necessary for device simulations. Different methods can be used to determine the band structure, for instance the atomistic DFT, the empirical

<sup>&</sup>lt;sup>2</sup>Near-equilibrium is a condition for which the carrier density can be accurately determined by Fermi-Dirac statics, see Eq. (1.1). This condition does not generally apply for ultra-scaled devices where strong lateral fields are present and dimensions are comparable to the mean-free-path for scattering [4]. In this case, 'far-from-equilibrium' transport models are required.

<sup>&</sup>lt;sup>3</sup>Actually,  $m_n^*$  is estimated from Eq. (2.3) itself, thus an accurate description of energy dispersion relation is crucial for obtaining correct simulation results.

Tight Binding (TB), the  $\mathbf{k} \cdot \mathbf{p}$  Method ( $\mathbf{k} \cdot \mathbf{p}$ ), and Nonparabolic Effective Mass Approximation (NP-EMA) [22], [24]. The  $\mathbf{k} \cdot \mathbf{p}$  method offers an intermediate level of approximation with a computational burden between DFT, TB and the least accurate NP-EMA. Thus,  $\mathbf{k} \cdot \mathbf{p}$  if often used for full quantum transport simulations and the NP-EMA method for the semiclassical transport approaches [22].

As we mentioned previously, due to their smaller  $m_n^*$ , InGaAs MOSFETs are more severely impacted by tunneling effects (leading to leakage currents) than their Si counterparts. A rigorous treatment of Source-Drain Tunneling (SDT) (which is expected to be the most prominent leakage contribution [22]) can be carried out only with full quantum simulations, that are commonly solved with the Nonequilibrium Green's Function (NEGF) method based on either TB,  $\mathbf{k} \cdot \mathbf{p}$ , or NP-EMA for the band structure calculation [22]. On the other hand, semiclassical methods based either on Multi Subband Monte Carlo (MSMC) [9] or QDD (such as that used by TCAD simulators) have severe limitations when it comes to SDT modeling [22].

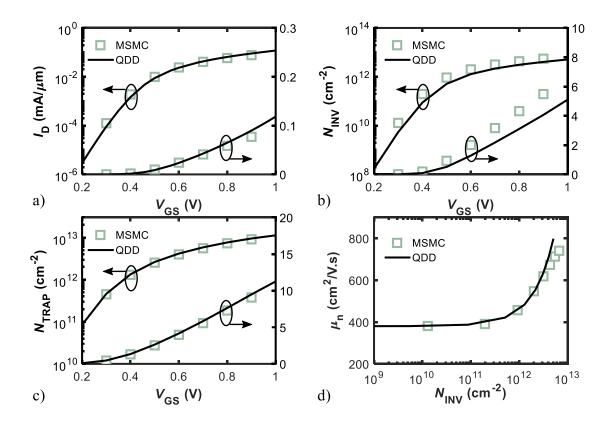

As far as mobility is concerned, the most accurate way to extract it accounting for all the scattering mechanisms is by using MSMC simulations. It has been shown in [26] that short devices still operate quite far from the ballistic limit, thus semiclassical approaches can accurately describe transport. The main limiting factor to mobility in the on-state (when there are no interface traps included [26]) is the Surface Roughness Scattering (SRS) [22].

On the TCAD side, a methodology to account for quasi-ballistic transport in DG-UTB devices was developed in [25]. The so-called ballistic mobility was then combined to the scattering-limited (semiclassical) mobility via a Matthiessen-like rule. In Section 2.4 we will present a different approach for mobility estimation in TCAD simulations that requires calibration with MSMC simulations to account for additional scattering due to ITs [55].

As we will see in Section 2.3, mobility measurements of InGaAs transistors via the split C - V method is affected by the trapped charge that overestimates the actual charge available for conduction [30]. Thus, simulation strategies are required in order to extract the intrinsic mobility of the devices [41].

### 2.2.5 Effects and Signatures of ITs and BTs

One of the most pressing challenge to the development of fast and reliable III-V MOSFETs is represented by ITs and BTs<sup>4</sup>. This is because unlike Si, III-Vs do not normally have a native oxide such as SiO<sub>2</sub>, therefore the phenomenon called "Fermi-level pinning" occurs [15], leading to a limited accumulation charge in the channel. ITs and BTs belong to the so-called "switching states" [16] that communicate with the channel (by exchanging charge) on a time scale comparable to that of measurement conditions. As the name suggests, ITs are those traps located at the interface between the semiconductor and the gate insulator whereas BTs are located in the oxide itself near the interface (few nanometers away) and interact with the semiconductor by quantum tunneling [17]. Both ITs and BTs lead to several drawbacks such as frequency dispersion in C - V measurements [17], [22], hysteresis in both I - V and C - V characteristics [18], [41], mobility reduction [22], [26], and threshold voltage ( $V_t$ ) and sub-threshold slope (SS) degradation [27].

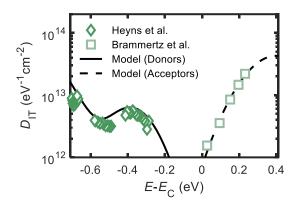

All in all, the reason why InGaAs MOSFETs are feasible is not because  $D_{IT}$  could be reduced to levels similar to that of Si/SiO<sub>2</sub> interface (i.e.,  $\sim 1 \times 10^{10} \, \mathrm{cm}^{-2}$ ) but rather thanks to the interface properties itself, that exhibits a charge neutrality level that is close to the  $E_C$  of InGaAs [27], thus rendering the traps in the band gap of the semiconductor donor-type and those *in* the conduction band itself acceptor-type<sup>5</sup>. Experimental data from [29], [30] showing trap states both in the energy range corresponding to InGaAs  $E_g$  and in its CB is collected in Fig. 2.3. According to the assumption of the charge neutrality level being located approximately at the conduction band minimum,  $E_C$  [27], the  $D_{IT}$  is modeled as a donor distribution in the band gap and an acceptor trap one in the conduction band, see Fig. 2.3. As mentioned previously, ITs and BTs give rise to a series of issues that reduce the performance gain of InGaAs MOSFETs over Si counterparts. As we will analyze in Section 2.3, one of the key signature of the presence of high

<sup>&</sup>lt;sup>4</sup>Traps are electrically active defects that interact with the semiconductor by exchanging charge and that effectively limit the performance of MOSFETs.

<sup>&</sup>lt;sup>5</sup>From basic semiconductor physics [28], when a trap energy state is located *below* the charge neutrality level it acts as a donor, i.e., it is positively charged when empty and neutral when occupied (by an electron). Conversely, a trap state *above* the neutrality level acts as an acceptor, i.e., it is neutral when empty and negatively charged when occupied (by an electron). Traps inducing a reduction in  $I_{ON}$  for n-type devices are the acceptors. This is why having a charge neutrality level far into the CB is important to avoid performance reductions.

Figure 2.3:  $D_{IT}$  distribution between InGaAs and Al<sub>2</sub>O<sub>3</sub>. Trap states below (above)  $E_C$  are modeled as donor-type (acceptor-type) [27]. Data is taken from [29], [30].

trap density is the frequency dispersion in C-V characteristics [17], [18] and also hysteresis, i.e., the difference between the upwards and downwards sweep when tracing either the I-V or C-V curves.

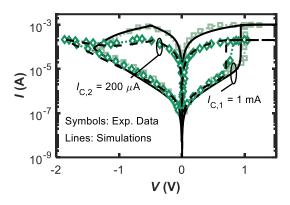

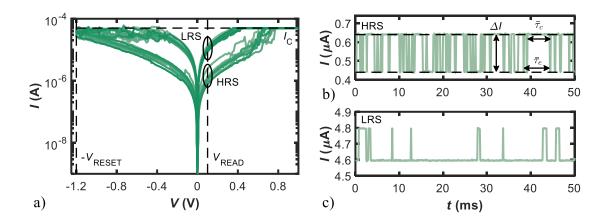

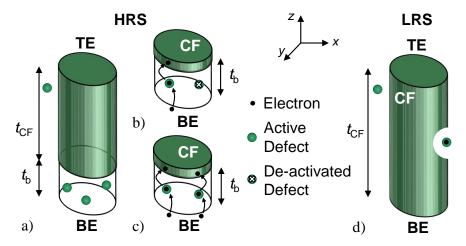

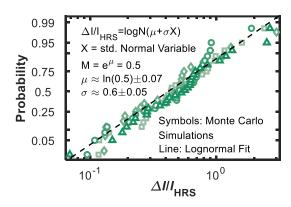

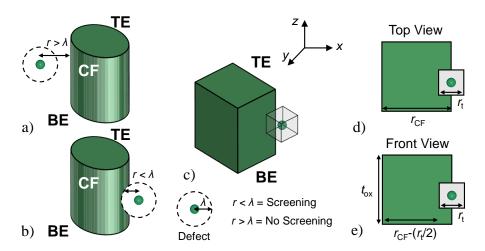

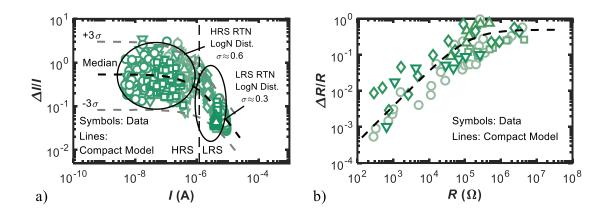

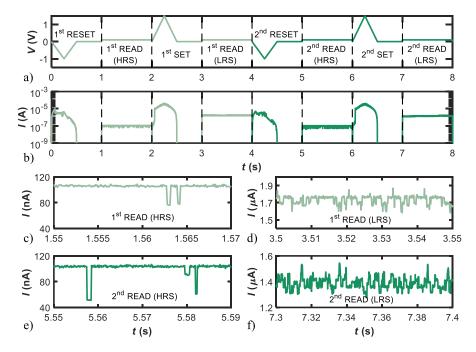

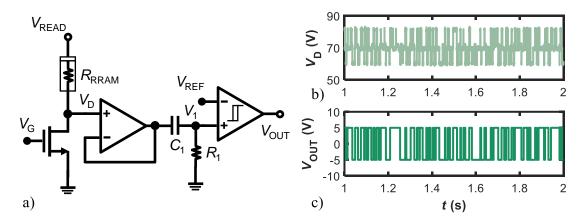

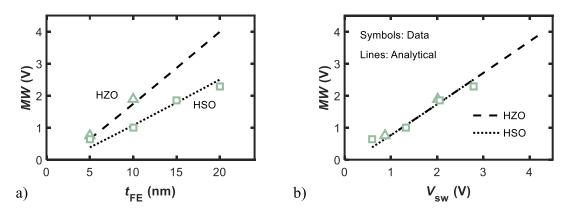

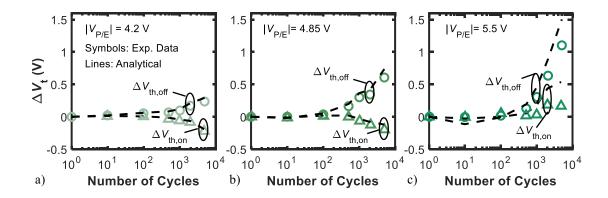

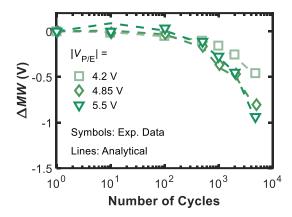

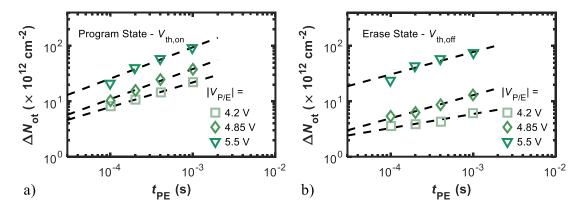

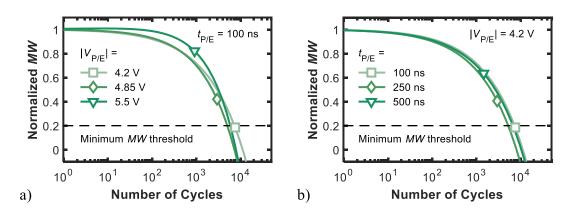

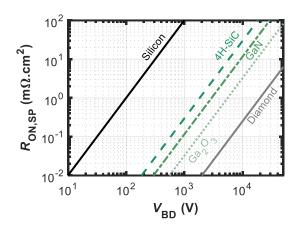

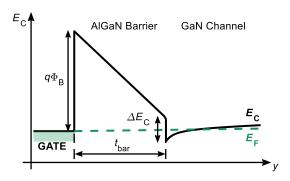

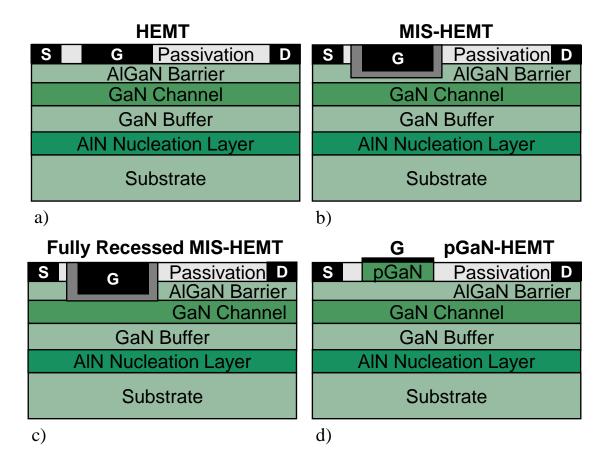

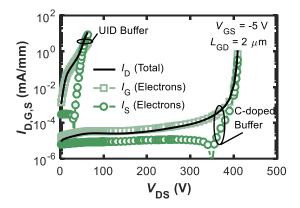

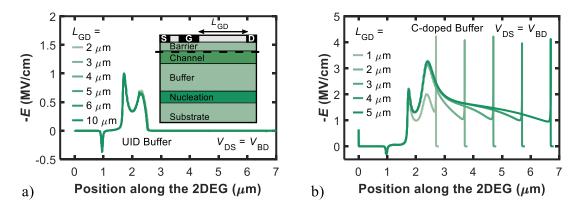

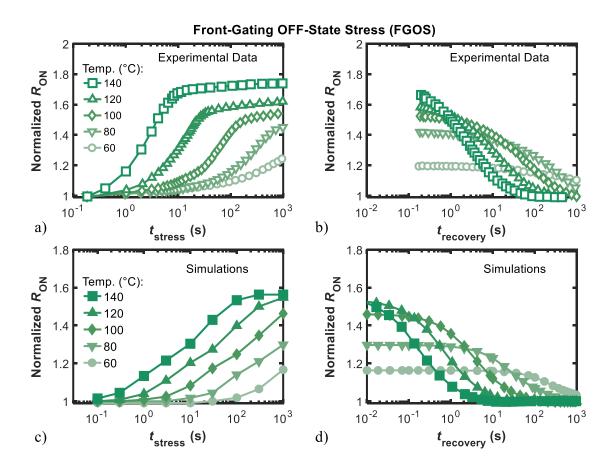

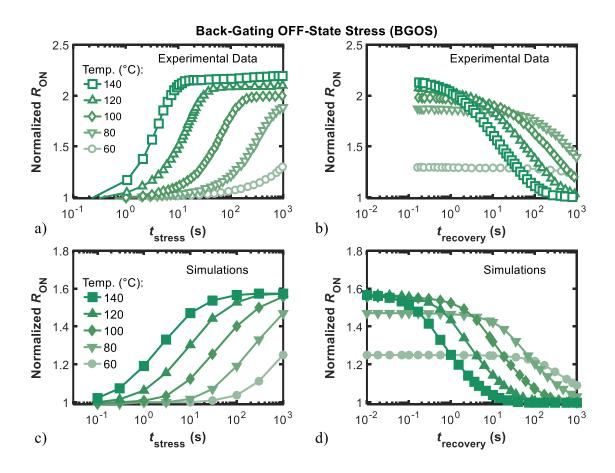

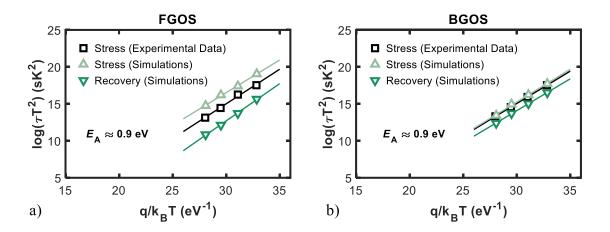

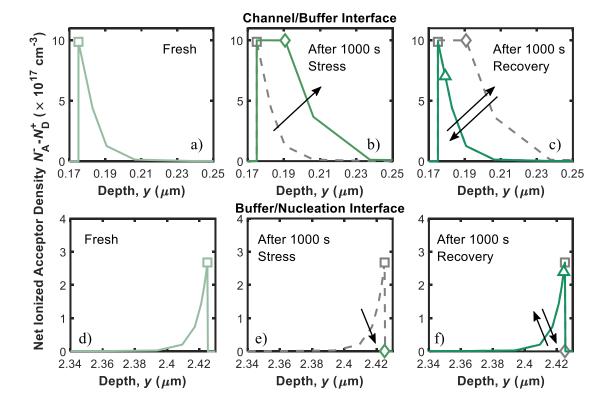

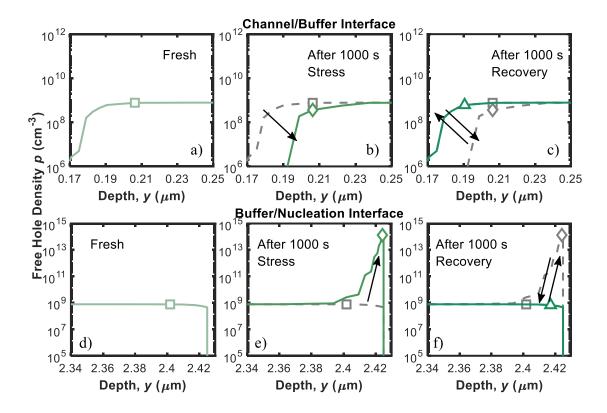

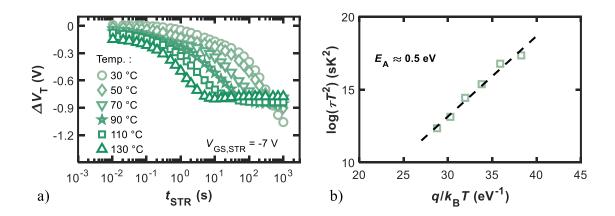

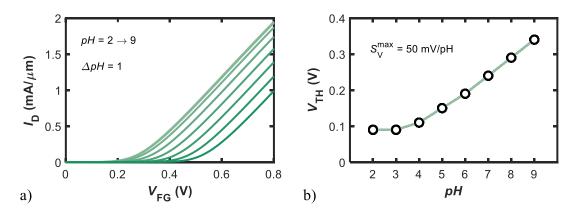

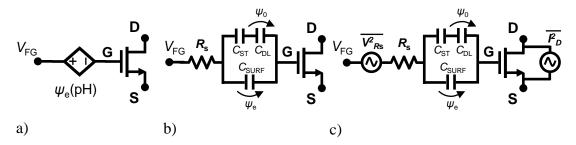

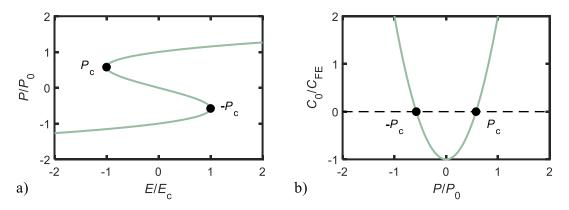

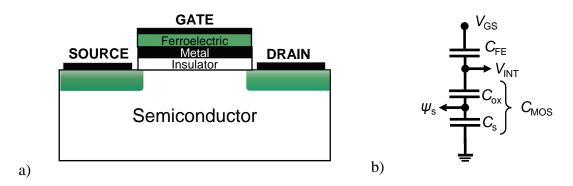

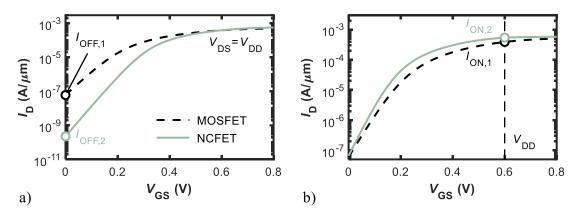

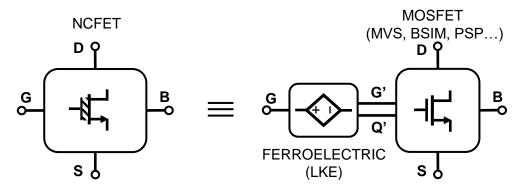

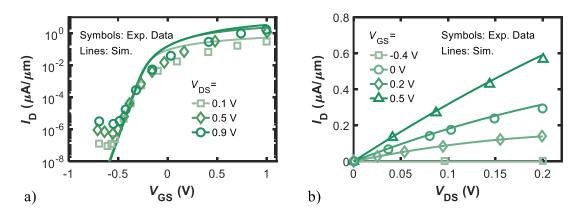

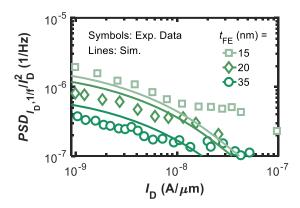

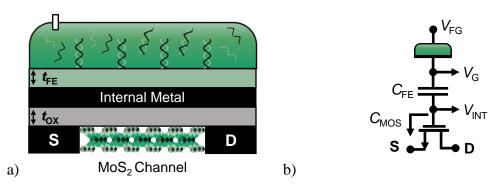

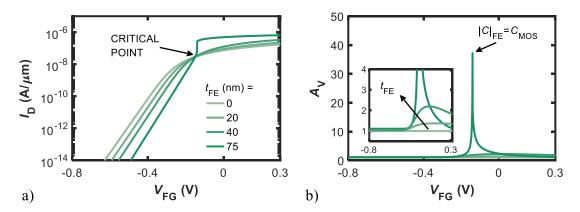

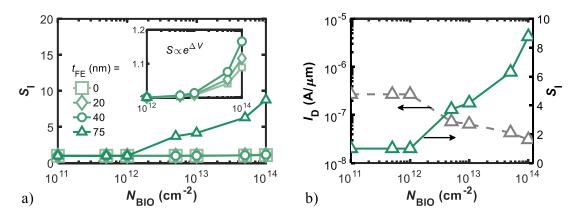

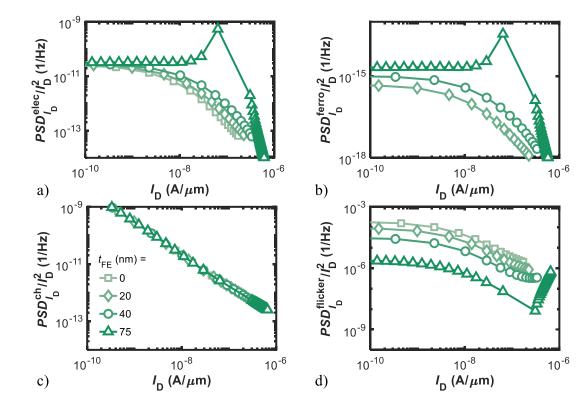

### 2.2.6 Variability in Nanoscale MOSFETs