Received 21 January 2019; accepted 27 February 2019. Date of publication 21 January 2019; date of current version 26 March 2019.

The review of this paper was arranged by Editor M. Liu.

Digital Object Identifier 10.1109/JEDS.2019.2902653

# Investigation of *I–V* Linearity in TaO<sub>x</sub>-Based RRAM Devices for Neuromorphic Applications

CHANGHYUCK SUNG<sup>®</sup> <sup>1</sup>, ANDREA PADOVANI<sup>®</sup> <sup>2,3</sup>, BASTIEN BELTRANDO<sup>4</sup>, DONGUK LEE<sup>1</sup>, MYUNGHOON KWAK<sup>®</sup> <sup>1</sup>, SEOKJAE LIM<sup>®</sup> <sup>1</sup>, LUCA LARCHER<sup>®</sup> <sup>5</sup>, VINCENZO DELLA MARCA<sup>®</sup> <sup>4</sup>, AND HYUNSANG HWANG<sup>®</sup> <sup>1</sup>

1 Center for Single Atom-Based Semiconductor Device and Department of Material Science and Engineering, Pohang University of Science and Technology, Pohang 37673, South Korea 2 MDLab s.r.l., 42122 Reggio Emilia, Italy 3 MDLSoft Inc., Santa Clara, CA 95054, USA

4 Aix-Marseille Université, IM2NP, CNRS, UMR 7334, 13397 Marseille, France

5 Dipartimento di Scienze e Metodi dell'Ingegneria, Universita di Modena e Reggio Emilia, 41125 Reggio Emilia, Italy

CORRESPONDING AUTHOR: H. HWANG (e-mail: hwanghs@postech.ac.kr)

This work was supported in part by the U.S. Army International Technology Center Pacific under Contract FA5209-17-C-0003, and in part by the MOTIE and KSRC Support Program for the Development of the Future Semiconductor Device under Grant 10067794.

**ABSTRACT** We perform experiments and device simulations to investigate the origin of current–voltage (I-V) linearity of  $TaO_x$ -based resistive switching memory (RRAM) devices for their possible application as electronic synapses. By using electrical characterization and simulations, we link the electrical characteristics (linear or nonlinear I-V) to the microscopic properties of the conductive filament (CF). Our findings indicate that the shape and the thermal properties of the CF region are crucial to achieve linear I-V characteristics. These results allow optimizing the I-V curve linearity of  $TaO_x$ -based RRAM devices, explaining the wide range of linear I-V characteristics experimentally observed on RRAM device obtained. When weight sum operation using SPICE simulations is performed, the read current is improved under the condition of linear I-V characteristics due to current loss minimization.

**INDEX TERMS** I-V linearity, neuromorphic system, resistive switching memory (RRAM), TaO<sub>x</sub>.

# I. INTRODUCTION

Neuromorphic computing systems are attracting considerable attention as replacements for the systems based on the conventional von-Neumann architecture, owing to their massively parallel, fault-tolerant, and low power consumption [1]. To implement a neuromorphic hardware system, synapse devices as well as CMOS-based neurons and peripheral circuit for storing weight data are required. Thus, many studies have been conducted to implement synapse devices by using phase change memory [2], magnetic memory [3], ferroelectric memory [4] and resistive switching memory (RRAM) [5]. In particular, RRAM that exhibits multi-level characteristics by controlling nanoscale conductive filament (CF) is promising due to their excellent scalability for constructing high-density arrays [6].

Many studies have reported multilevel characteristics achieved during potentiation or depression in the weight update operations [7]–[11]. On the other hand, the

weight sum operation (vector-matrix multiplication) using RRAM-based cross-point arrays, is performed by summing the current, which means that the conductance of each synapse device is multiplied by the read voltage [12]. In this weight sum operation, all synapse devices in the cross-point array participate in the computation according to Kirchhoff's Law. However, distortion of read voltage occurs due to parasitic metal wire resistance, resulting in dependence of the read voltage on the location of the synaptic device in crosspoint array [13], [14]. For this reason, the current-voltage (I-V) linearity of the synaptic devices is required to minimize read current loss during the weight sum operation. Thus, the optimization of the I-V linearity in a wide range of compliance current  $(I_{comp})$  is required, which needs to understand the physical mechanisms and process engineering. In this scenario, several works have investigated the correlation between the density of oxygen vacancies (V<sub>0</sub>) in the CF and the I-V linearity [15], [16]. The effect of I-V linearity on the pattern recognition accuracy has also been investigated [17].

In this work, we compare two different RRAM device stacks and use experiments and simulations to link the degree of I–V linearity to the material and CF properties. This study presents a guideline for device engineering to achieve linear I–V characteristics. In addition, read current loss as a function of array size and parasitic metal wire resistance is evaluated using SPICE simulations.

## II. EXPERIMENT

Two different RRAM device stacks using Ta and Ti as oxygen exchange layer were considered in this study. All devices were fabricated in 250-nm via-hole structure. For the isolation layer, 150-nm-thick SiO<sub>2</sub> sidewall layer was deposited on a Pt/TiN/SiO<sub>2</sub>/Si substrate via plasma-enhanced chemical vapor deposition. Subsequently, 250-nm via-holes were formed via lithographic and etching process. A 5-nm tantalum oxide (Ta2O5-x) layer was deposited on top of a Pt bottom electrode (BE) using RF magnetron sputtering with a stoichiometric Ta<sub>2</sub>O<sub>5</sub> target. Then, 10-nm layers of Ta and Ti were deposited separately through DC magnetron sputtering with a Ta and Ti target followed by the deposition of a 10-nm-thick W top electrode, respectively. The voltage for all measurements was applied to the top electrode. RRAM operations were simulated using the Ginestra software package [18], [19] that includes all the physical mechanisms relevant for the operation and reliability of RRAM devices: carriers trapping and transport, the induced power dissipation and associated temperature increase (calculated by solving Fourier's heat flow equation with Dirichlet boundary conditions at the electrodes), the generation, recombination, and diffusion of V<sub>0</sub> and interstitial ions (O<sup>-</sup>) [20]. Charge transport is described considering tunneling (direct/Fowler Nordheim tunneling and trap-assisted tunneling (TAT) [21]) and drift contributions. The change in the dominant mechanism from TAT to drift that occurs in presence of high O vacancy densities (i.e., the CF region) is automatically considered. High Vo densities lead to the formation of defect sub-bands in which the drift transport is still calculated in the TAT framework by setting the tunneling and lattice relaxation probabilities equal to one [20], which give the expected Ohmic-like conduction.

In this work, the typical simulated volume is  $10\times10\times5$  nm<sup>3</sup>, being 5 nm the thickness of the Ta<sub>2</sub>O<sub>5-x</sub> oxide, which is enough to correctly describe a single CF.

# III. RESULTS AND DISCUSSION

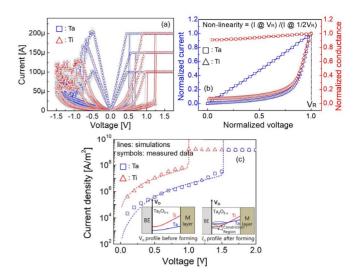

Figure 1(a) shows the I-V characteristics of the Ti/Ta<sub>2</sub>O<sub>5-x</sub> and Ta/Ta<sub>2</sub>O<sub>5-x</sub> devices after forming, obtained by imposing a  $I_{comp}$  of 100, 150 and 200  $\mu$ A. The bipolar switching behavior is attributed to the formation and rupture of a CF composed of  $V_o$  generated during the initial forming operation. The CF properties, i.e., the  $V_o$  profiles were determined by the reactive metal layer properties (e.g., electronegativity) and the forming operation [22]. Both Ti- and Ta-based

FIGURE 1. (a) I-V characteristics of  $TaO_x$ -based RRAM devices with Ta and Ti electrodes. (b) Comparison of normalized I-V and G-V characteristics of LRS between  $Ta/Ta_2O_{5-x}$  and  $Ti/Ta_2O_{5-x}$  for  $100~\mu$ A of compliance current. (c) Measured (symbols) and simulated (lines) forming I-V characteristics of both  $Ta/Ta_2O_{5-x}$  and  $Ti/Ta_2O_{5-x}$ . The inset is a schematic diagram of the  $V_0$  profile before and after forming.

devices show good resistive switching (RS) behavior, see Fig. 1 (a). However, in the low-resistance state (LRS) the Ti/Ta<sub>2</sub>O<sub>5-x</sub> device shows nonlinear *I-V* and conductancevoltage (G-V) characteristics, whereas that of the Ta/Ta<sub>2</sub>O<sub>5-x</sub> device exhibits linear I-V and G-V, see Fig. 1 (b). To understand the origin of these differences, we analyzed the CF properties of the Ta- and Ti- devices before and after forming using both ad-hoc experiments and simulations. Figure 1 (c) shows the measured (symbols) and simulated (lines) I-V characteristics during the forming of both devices. The higher current of the Ti/Ta<sub>2</sub>O<sub>5-x</sub> device before the forming process indicates a higher initial V<sub>0</sub> density  $(2.5 \times 10^{20} \text{ cm}^{-3})$  compared to that of Ta/Ta<sub>2</sub>O<sub>5-x</sub>(2×10<sup>19</sup> cm<sup>-3</sup>), as confirmed by simulations. Moreover, the highly reactive Ti electrode is expected to induce a highly asymmetric Vo profile with a constriction close to the BE owing to its oxygen scavenging ability. On the contrary, a much more uniform V<sub>0</sub> profile is expected for the Ta-Ta<sub>2</sub>O<sub>5-x</sub> device as schematically depicted in the insets of Fig. 1(c). The highly non-uniform V<sub>o</sub> profile in the Ti/Ta<sub>2</sub>O<sub>5-x</sub> stack is expected to be maintained also after forming (depending on the compliance) and could be the origin of the differences observed with respect to Ta-based devices.

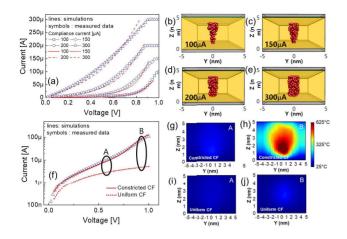

We used simulations to investigate and understand the differences observed in the  $I_{\rm comp}$ -dependent LRS I-V characteristics of the Ti- and Ta-based devices. In addition, we only used simulations to extract the CF properties (shape, size,  $V_{\rm o}$  density, etc...) allowing reproduction of the experimental data without full forming simulations. Figure 2(a) shows the LRS currents measured and simulated for the Ti/Ta<sub>2</sub>O<sub>5-x</sub> stack. Simulations reproduce the experimental data at  $I_{\rm comp} = 100/150/200/300~\mu{\rm A}$  when considering the CFs shown in Fig. 2(b)-(e). The results

VOLUME 7, 2019 405

FIGURE 2. (a) Measured (symbols) and simulated (lines) LRS I-V characteristics of Ti/Ta<sub>2</sub>O<sub>5-x</sub> at different compliance currents. (b)-(e) 3D maps of the V<sub>0</sub> distributions (CF) allowing reproduction of the experimental data in (a). (f) Comparison of I-V characteristics simulated considering (solid line) constricted and (dashed line) uniform CFs. (g)-(j) Temperature maps of (top) constricted CF and (bottom) uniform CF (extracted from I-V characteristics of region A and B in Fig. 2 (f)). Different temperatures depending on CF states are shown (A-B). The state of the constricted CF in the temperature map is the same as the 3D map of the V<sub>0</sub> distributions with the 100  $\mu$ A of compliance current.

indicate that the I-V non-linearity at low  $I_{comp}$  is due to the conical shape of the CF and the thermal properties (i.e., thermal conductivity) of the RS material. The filament constriction close to the BE induces a high local power dissipation associated with the current flow. The generated heat is not removed efficiently because of the low thermal conductivity of Ta<sub>2</sub>O<sub>5</sub> (0.7W m<sup>-1</sup>K<sup>-1</sup> [23]), causing a significant temperature increase, as shown in Fig. 2(h); this eventually leads to the super linear increase of the current, from A to B in Fig. 2(f). This is a consequence of the strong dependence of the TAT conduction mechanism - still dominating in the constriction region – on the temperature [21]. Simulations performed considering a uniform CF confirmed that the constriction-induced local temperature increase was at the bases of the observed non-linearity. Indeed, the I-V characteristics simulated in the uniform CF case is linear (Fig. 2(f)), and the temperature increase is low, as shown in Fig. 2(j). When higher  $I_{comp}$  are imposed, the conical CF gets wider and more metallic, and its shape changed from conical to cylindrical due to the massive V<sub>0</sub> generation, see in Fig. 2(e). This allows more efficient removal of the heat generated by the current flow and the corresponding I-Vcharacteristics become linear, see in Fig. 2(a).

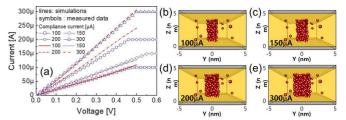

On the contrary, the LRS currents measured on the Ta/Ta<sub>2</sub>O<sub>5-x</sub> stack were reproduced by considering a uniform CF independently of  $I_{comp}$ , as shown in Fig. 3(a). As discussed above, this allows a better dissipation of the generated heat, which in turns results in a higher I-V curve linearity. Increasing the  $I_{comp}$  leads to a wider and more metallic CF (Fig. 3(b)-(e)).

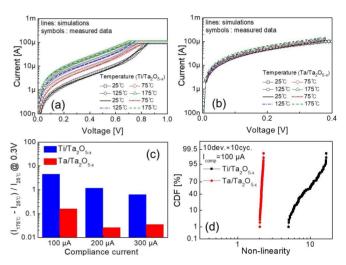

To further investigate the properties of the CFs formed in Ti- and Ta-based devices, we performed temperaturedependent measurements of the LRS currents at different

FIGURE 3. (a) Measured (symbols) and simulated (lines) LRS I-V characteristics of  $Ta/Ta_2O_{5-X}$  for various compliance current. (b)-(e) 3D maps of the  $V_0$  distributions (CF) allowing reproduction of the experimental data as in (a).

FIGURE 4. Temperature-dependent LRS *I–V* measured (symbols) and simulated (lines) for (a) Ti/Ta<sub>2</sub>O<sub>5-x</sub> and (b) Ta/Ta<sub>2</sub>O<sub>5-x</sub> devices. (c) Temperature dependence of LRS current for different compliance current. (d) Distribution of non-linearity for the Ti/Ta2O5-x and Ta/Ta2O5-x device.

$I_{\text{comp}}$ . Figure 4(a) and (b) show the results for the low  $I_{\text{comp}}$ of 100  $\mu$ A. A large temperature dependence was observed in the Ti/Ta<sub>2</sub>O<sub>5-x</sub> stack, as shown in Fig. 4(a), indicating that the charge transport was still dominated by defect-assisted mechanisms such as TAT, even after forming [20], [21]. Simulations confirm that the observed temperature dependence is mainly due to TAT transport through defects located in the constricted portion of the CF, with an additional contribution due to the temperature dependence of the bandgap in the highly sub-stoichiometric  $Ta_2O_{5-x}$  (~3meV/K). Conversely, the LRS current measured on the Ta/Ta<sub>2</sub>O<sub>5-x</sub> device after forming at 100µA exhibits much lower temperature dependence, as shown in Fig. 4(b). This is consistent with the drift-driven charge transport expected in a quasimetallic CF, as confirmed by simulations. As expected, the temperature dependence of the LRS current in Ti/Ta<sub>2</sub>O<sub>5-x</sub> devices reduces significantly with increasing  $I_{comp}$ , as shown in Fig. 4(c), which agrees with the creation of a more uniform and metallic CF, as shown by simulations in Fig. 2. In the case of the  $Ta/Ta_2O_{5-x}$  device, the LRS I-V characteristics showed approximately the same I-V curve temperature dependence as a function of I<sub>comp</sub> much lower than that in

406 VOLUME 7, 2019

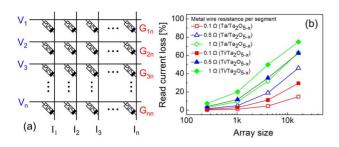

FIGURE 5. (a) Schematic of RRAM-based synapse device cross-point array. (b) Read current loss as depending on cross-point array size under different parasitic metal wire resistance.

the case of Ti/Ta<sub>2</sub>O<sub>5-x</sub>, consistently with a quasi-metallic CF (Fig. 4(c)). It should be noted that the conduction mechanisms allowing consistently describing the results in Figs. 2, 3, and 4 (i.e., TAT and drift) are the ones frequently reported in the literature for HRS and LRS states [24], although some groups reported Poole-Frenkel [25], [26]. In addition, Fig. 4 (d) presents the device-to-device and cycle-to-cycle variations of Ti/Ta<sub>2</sub>O<sub>5-x</sub> and Ta/Ta<sub>2</sub>O<sub>5-x</sub> devices as a function of non-linearity (non-linearity = I @  $V_R$  / I @ 1/2 $V_R$ , as shown in Fig. 1 (b)). The quasi-metallic CF of the Ta/Ta<sub>2</sub>O<sub>5-x</sub> device guarantees a linear *I–V* characteristics (non-linearity =  $\sim$  2).

We finally investigated the output read current across the array using SPICE simulations. In neuromorphic cross-point array systems, the read voltage for vector-matrix multiplication is applied to each word line (Fig. 5 (a)). The output current flowing from the bit line is given by the sum of the currents driven by the activated synapses. The current driven by all cells depends on the actual read signal applied, which in turn depends on the cell position in the array due to the parasitic resistance. To evaluate this effect, we considered synaptic devices in the array were randomly trained in HRS or LRS. The read voltage to obtain a similar conductance value is applied to each of the two synaptic device arrays (LRS =  $\sim 200 \mu S$ , HRS =  $\sim 10 \mu S$  at 0.88 V (Ti/Ta<sub>2</sub>O<sub>5-x</sub>), 0.44 V (Ta/Ta<sub>2</sub>O<sub>5-x</sub>)). The read current is evaluated at the bit line farthest from the read voltage source. The read current loss, as a function of the read current at the bit line, is defined as  $(I_{Ideal}-I_{Real}/I_{Ideal}) \times 100$ . In our simulations, we set the parasitic metal wire resistance per segment (each end of a segment typically has a synaptic device attached) to 0  $\Omega$  for the ideal read current ( $I_{\text{Ideal}}$ ) and between 0.1 and 1  $\Omega$  for the real read current ( $I_{Real}$ ). Figure 5 (b) shows the read current loss for various cross-point array size ranging from  $16 \times 16$  to  $128 \times 128$ , under different parasitic metal wire resistance. The result shows an increase of the read current loss as the array size increases. This means that read voltage is not fully applied to the synaptic device due to the parasitic metal wire resistance, which leads to a degradation of the read current. Although the degree of read current degradation increases with the parasitic metal wire resistance, Ta/Ta<sub>2</sub>O<sub>5-x</sub> devices, which guaranteed linear I-V characteristics, exhibited much lower current loss

than the Ti/ $Ta_2O_{5-x}$  devices. Therefore, to mitigate read current loss in high-density cross-point arrays, I-V linearity is crucial to achieving the accurate weight sum operations in neuromorphic application.

### IV. CONCLUSION

We performed experiments and simulations to investigate the origin of the *I-V* linearity in TaO<sub>x</sub>-based RRAM devices. Our results revealed that the shape and properties of the CF including the thermal conductivity of the RS film play a crucial role to ensure linear *I-V* characteristics. In particular, the constriction in a conical-like CF and the consequent poor heat dissipation are the major obstacles to achieve linear *I-V* characteristics that are instead obtained with a uniform and more metallic CF. Our findings provide fundamental insights into how to manipulate the material properties for optimizing the *I-V* linearity in RRAM synapses. Finally, SPICE simulations showed that *I-V* linearity allows mitigating the parasitic wire resistance in cross-point RRAM synapses arrays, mitigating the read current loss in neuromorphic system.

#### REFERENCES

- C. Mead, "Neuromorphic electronic systems," *Proc. IEEE*, vol. 78, no. 10, pp. 1629–1636, Oct. 1990. doi: 10.1109/5.58356.

- [2] G. W. Burr et al., "Experimental demonstration and tolerancing of a large-scale neural network (165 000 synapses) using phasechange memory as the synaptic weight element," *IEEE Trans. Electron Devices*, vol. 62, no. 11, pp. 3498–3507, Nov. 2015. doi: 10.1109/TED.2015.2439635.

- [3] A. F. Vincent et al., "Spin-transfer torque magnetic memory as a stochastic memristive synapse for neuromorphic systems," *IEEE Trans. Biomed. Circuits Syst.*, vol. 9, no. 2, pp. 166–174, Apr. 2015. doi: 10.1109/TBCAS.2015.2414423.

- [4] M. Jerry et al., "Ferroelectric FET analog synapse for acceleration of deep neural network training," in *IEEE IEDM Tech. Dig.*, Dec. 2017, pp. 6.2.1–6.2.4. doi: 10.1109/IEDM.2017.8268338.

- [5] S. Jo et al., "Nanoscale memristor device as synapse in neuromorphic systems," Nano Lett., vol. 10, no. 4, pp. 1297–1301, 2010. doi: 10.1021/nl904092h.

- [6] B. Govoreanu et al., "10 × 10 nm<sup>2</sup> Hf/HfO<sub>x</sub> crossbar resistive RAM with excellent performance, reliability and low-energy operation," in *IEEE IEDM Tech. Dig.*, Dec. 2011, pp. 31.6.1–31.6.4. doi: 10.1109/IEDM.2011.6131652.

- [7] J. Woo et al., "Linking conductive filament properties and evolution to synaptic behavior of RRAM devices for neuromorphic applications," *IEEE Electron Device Lett.*, vol. 38, no. 9, pp. 1220–1223, Sep. 2017. doi: 10.1109/LED.2017.2731859.

- [8] A. Padovani, J. Woo, H. Hwang, and L. Larcher, "Understanding and optimization of pulsed SET operation in HfO<sub>x</sub>-based RRAM devices for neuromorphic computing applications," *IEEE Electron Device Lett.*, vol. 39, no. 5, pp. 672–675, May 2018. doi: 10.1109/LED.2018.2821707.

- [9] J. Woo et al., "Improved synaptic behavior under identical pulses using AlO<sub>x</sub> /HfO<sub>2</sub> bilayer RRAM array for neuromorphic systems," *IEEE Electron Device Lett.*, vol. 37, no. 8, pp. 994–997, Aug. 2016. doi: 10.1109/LED.2016.2582859.

- [10] W. Wu et al., "Improving analog switching in HfO<sub>x</sub>-based resistive memory with a thermal enhanced layer," *IEEE Electron Device Lett.*, vol. 38, no. 8, pp. 1019–1022, Aug. 2017. doi: 10.1109/LED.2017.2719161.

- [11] S. Yu et al., "A neuromorphic visual system using RRAM synaptic devices with sub-pJ energy and tolerance to variability: Experimental characterization and large-scale modeling," in *IEDM Tech. Dig.*, Dec. 2012, pp. 10.4.1–10.4.4. doi: 10.1109/IEDM.2012.6479018.

VOLUME 7, 2019 407

- [12] M. Hu et al., "Memristor crossbar-based neuromorphic computing system: A case study," IEEE Trans. Neural Netw. Learn. Syst., vol. 25, no. 10, pp. 1864–1878, Oct. 2014. doi: 10.1109/TNNLS.2013.2296777.

- [13] S. Yu et al., "Scaling-up resistive synaptic arrays for neuro-inspired architecture: Challenges and prospect," in *IEDM Tech. Dig.*, Dec. 2016, pp. 17.3.1–17.3.4. doi: 10.1109/IEDM.2015.7409718.

- [14] P.-Y. Chen, X. Peng, and S. Yu, "NeuroSim: A circuit-level macro model for benchmarking neuro-inspired architectures in online learning," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 37, no. 12, pp. 3067–3080, Dec. 2018. doi: 10.1109/TCAD.2018.2789723.

- [15] E. A. Miranda, C. Walczyk, C. Wenger, and T. Schroeder, "Model for the resistive switching effect in HfO<sub>2</sub> MIM structures based on the transmission properties of narrow constrictions," *IEEE Electron Device Lett.*, vol. 31, no. 6, pp. 609–611, Jun. 2010. doi: 10.1109/LED.2010.2046310.

- [16] R. Degraeve et al., "Generic learning of TDDB applied to RRAM for improved understanding of conduction and switching mechanism through multiple filaments," in *IEEE IEDM Tech. Dig.*, Dec. 2010, pp. 28.4.1–28.4.4. doi: 10.1109/IEDM.2010.5703438.

- [17] C. Sung et al., "Effect of conductance linearity and multi-level cell characteristics of TaOx-based synapse device on pattern recognition accuracy of neuromorphic system," Nanotechnology, vol. 29, no. 11, 2018. Art. no. 115203. doi: 10.1088/1361-6528/aaa733.

- 2018, Art. no. 115203. doi: 10.1088/1361-6528/aaa733.

[18] *Ginestra*<sup>TM</sup> *Software*. Accessed: Jan. 12, 2018. [Online]. Available: www.mdlsoft.com

- [19] L. Larcher, A. Padovani, and L. Vandelli, "A simulation framework for modeling charge transport and degradation in high-k stacks," *J. Comput. Electron.*, vol. 12, no. 4, pp. 658–665, Dec. 2013. doi: 10.1007/s10825-013-0526-z.

- [20] A. Padovani, L. Larcher, O. Pirrotta, L. Vandelli, and G. Bersuker, "Microscopic modeling of  $HfO_X$  RRAM operations: From forming to switching," *IEEE Trans. Electron Devices*, vol. 62, no. 6, pp. 1998–2006, Jun. 2015. doi: 10.1109/TED.2015.2418114.

- [21] L. Vandelli et al., "A physical model of the temperature dependence of the current through SiO<sub>2</sub>/HfO<sub>2</sub> stacks," *IEEE Trans. Electron Devices*, vol. 58, no. 9, pp. 2878–2887, Sep. 2011. doi: 10.1109/TED.2011.2158825.

- [22] D. C. Gilmer et al., "Asymmetry, vacancy engineering and mechanism for bipolar RRAM," in Proc. IEEE Int. Memory Workshop, May 2012, pp. 1–4. doi: 10.1109/IMW.2012.6213649.

- [23] C. D. Landon et al., "Thermal transport in tantalum oxide films for memristive applications," Appl. Phys. Lett., vol. 107, no. 2, 2015, Art. no. 023108. doi: 10.1063/1.4926921.

- [24] S. Yu, X. Guan, and H.-S. P. Wong, "On the stochastic nature of resistive switching in metal oxide RRAM: Physical modeling, Monte Carlo simulation, and experimental characterization," in *IEEE IEDM Tech. Dig.*, Dec. 2011, pp. 17.3.1–17.3.4. doi: 10.1109/IEDM.2011.6131572.

- [25] S. Ambrogio et al., "Statistical fluctuations in HfO<sub>x</sub> resistive-switching memory: Part II—Random telegraph noise," *IEEE Trans. Electron Devices*, vol. 61, no. 8, pp. 2920–2927, Aug. 2014. doi: 10.1109/TED.2014.2330202.

- [26] C. Walczyk et al., "Impact of temperature on the resistive switching behavior of embedded HfO<sub>2</sub>-based RRAM devices," *IEEE Trans. Electron Devices*, vol. 58, no. 9, pp. 3124–3131, Sep. 2011. doi: 10.1109/TED.2011.2160265.

**CHANGHYUCK SUNG** received the B.S. degree from the Department of Materials Science and Engineering, Pohang University of Science and Technology, Pohang, South Korea, in 2015, where he is currently pursuing the Ph.D. degree.

ANDREA PADOVANI received the graduation degree in electronic engineering from the University of Modena and Reggio Emilia, Italy, and the Ph.D. degree from the University of Ferrara, Italy. After holding several positions with the University of Modena and Reggio Emilia, he co-founded MDLab s.r.l., Italy, in 2013 and MDLsoft, USA, in 2017, two companies developing and marketing the commercial semiconductor device simulation software Ginestra. He has authored and co-authored over 140 technical

papers. His research interests include the modeling of dielectric degradation and breakdown of transistors and the modeling of nonvolatile memories. He is/has been a Committee Member of IEEE International Integrated Reliability Workshop, IEEE International Reliability Physics Symposium, International Symposium on Very Large Scale Integration Technology, Systems and Applications and of the European Symposium on Reliability of Electron Devices, and Failure Physics and Analysis.

**BASTIEN BELTRANDO**, photograph and biography not available at the time of publication.

**DONGUK LEE**, photograph and biography not available at the time of publication.

**MYUNGHOON KWAK**, photograph and biography not available at the time of publication.

**SEOKJAE LIM**, photograph and biography not available at the time of publication.

**LUCA LARCHER** received the graduation degree in electronic engineering from the University of Padova, Italy, in 1998, and the Ph.D. degree in information engineering from the University of Modena and Reggio Emilia in 2002.

He is currently a Full Professor of electronics with the University of Modena and Reggio Emilia. He has authored and co-authored 1 book and 2 book chapters, and over 230 technical papers published on international journals and proceedings of international conferences. His research interests

include the modeling and characterization of non-volatile memory devices and of physical mechanisms governing the charge transport and degradation in high-k dielectrics, the characterization and design of integrated circuits for both communications and energy harvesting applications, and printed technology solutions for audio/automotive transducers.

Dr. Larcher was on the technical and executive committees of the IEEE-IEDM from 2006 to 2007 and from 2013 to 2015, IEEE-IRPS from 2011 to 2012 and from 2017 to 2019, and IIRW from 2013 to 2018. He served as the Technical Program Chair for 2017 conferences.

VINCENZO DELLA MARCA was born in Modena, Italy, in 1983. He received the master's degree in electrical engineering from the University of Modena and Reggio Emilia, Modena, in 2008, and the Ph.D. degree from Aix-Marseille University, Marseille, France, in collaboration with STMicroelectronics and CEA-Leti, Grenoble, in 2013

He is currently an Associate Professor with Aix-Marseille University. His research interests include electrical characterization and modeling of

nonvolatile memories for embedded applications.

**HYUNSANG HWANG** received the Ph.D. degree in material science from the University of Texas at Austin, Austin, USA, in 1992.

He was with LG Semiconductor Corporation. He was a Professor of materials science and engineering with the Gwangju Institute of Science and Technology, Gwangju, South Korea, in 1997. In 2012, he joined the Materials Science and Engineering Department, Pohang University of Science and Technology, Pohang, South Korea. He has published over 360 journal papers and

32 IEDM/VLSI technology papers. His current research interests include neuromorphic device, ReRAM, and selector devices.

408 VOLUME 7, 2019