This is the peer reviewd version of the followng article:

Experimental and Numerical Analysis of OFFState Bias Induced Instabilities in Vertical GaNon-Si Trench MOSFETs / Zagni, N.; Fregolent, M.; Verzellesi, G.; Bergamin, F.; Favero, D.; De Santi, C.; Meneghesso, G.; Zanoni, E.; Huber, C.; Meneghini, M.; Pavan, P.. - In: IEEE TRANSACTIONS ON POWER ELECTRONICS. - ISSN 0885-8993. - 39:11(2024), pp. 14295-14303. [10.1109/TPEL.2024.3441712]

Terms of use:

The terms and conditions for the reuse of this version of the manuscript are specified in the publishing policy. For all terms of use and more information see the publisher's website.

27/09/2024 09:39

# Experimental and Numerical Analysis of OFF-State Bias Induced Instabilities in Vertical GaNon-Si Trench MOSFETs

Nicolò Zagni, *Member, IEEE*, Manuel Fregolent, Giovanni Verzellesi, *Senior Member, IEEE*, Francesco Bergamin, Davide Favero, Carlo De Santi, *Member, IEEE*, Gaudenzio Meneghesso, *Fellow, IEEE*, Enrico Zanoni, *Life Fellow, IEEE*, Christian Huber, Matteo Meneghini, *Senior Member, IEEE*, and Paolo Pavan, *Senior Member, IEEE*

Abstract-We analyzed the threshold-voltage dynamic instabilities induced by OFF-state stress in pseudo-vertical **MOSFETs** GaN-on-Si Trench (TMOS). Extensive measurements revealed that OFF-state stress experiments induce a progressive increase of threshold voltage ( $V_{T}$ ), that is fully recoverable only after high-temperature cycles, so that it can appear as permanent degradation at room temperature.  $V_{\rm T}$  increase is found to be strongly affected by drain bias and negligibly influenced by gate bias (below threshold). Activation energy (E<sub>A</sub>) extracted from hightemperature V<sub>T</sub> recovery experiments was determined to be ≈1 eV. We further characterized pseudo-vertical p-n junction diodes fabricated onto the same wafer as the TMOS's by means of capacitance iso-thermal spectroscopy (C-ITS). This experiment revealed depletion capacitance (CDEP) instabilities with the same EA as that characterizing the V<sub>T</sub> instability, leading to the conclusion that trap states present in the epitaxy are the cause of both observations. Numerical device simulations guided the physical interpretation of the observed phenomena, i.e., that donor traps at 1 eV from the conduction band and localized in the p-layer can lead to both  $V_{T}$  and  $C_{DEP}$  instabilities in the TMOS and in the p-n diode, respectively, by dynamically modulating the effective p-type doping density in the former and the effective depletion layer width in the latter.

# Index Terms—Vertical GaN, Trench MOSFET, OFF-State Stress, Stability, Reliability, Trapping.

This work has been carried out in the framework of the European Project "YESvGaN". The project has received funding from the Electronic Component Systems for European Leadership Joint Undertaking (ECSEL JU), under grant agreement No. 101007229. This Joint Undertaking receives support from the European Union's Horizon 2020 Research and Innovation Programme, and Germany, France, Belgium, Austria, Sweden, Spain, and Italy.

N. Zagni, and P. Pavan are with the Department of Engineering "Enzo Ferrari", University of Modena and Reggio Emilia, 41125, Modena, Italy. (N. Zagni and M. Fregolent contributed equally to this work.) (*Corresponding authors*: N. Zagni and M. Fregolent. E-mail: nicolo.zagni@unimore.it, manuel.fregolent@unipd.it).

M. Fregolent, F. Bergamin, D. Favero, C. De Santi, M. Meneghini, G. Meneghesso, and E. Zanoni are with the Department of Information Engineering, University of Padova, Via Giovanni Gradenigo 6B, 35131 Padova, Italy.

G. Verzellesi is with the Department of Sciences and Methods for Engineering (DISMI), University of Modena and Reggio Emilia, 42122, Reggio Emilia, Italy and, also, with the EN&TECH Center, University of Modena and Reggio Emilia, 42122, Reggio Emilia, Italy.

C. Huber is with the Advanced Technologies and Micro Systems Department, Robert Bosch GmbH, 71272, Renningen, Germany.

#### I. INTRODUCTION

VERTICAL GaN-on-Si devices are a potential cost-effective alternative compared to Si and SiC counterparts for high power switching applications [1], [2]. While GaN-on-Si pseudo-vertical diodes with breakdown voltage ( $V_{BR}$ ) in the 800-900 V range [3], [4] and with avalanche capability [5] have already been proven in research labs, the challenge of delivering high performance and reliability on large-scale wafers (> 200 mm) is yet to be overcome [6]. Moreover, vertical transistors such as Trench MOSFETs (TMOS's) present further hurdles compared to diodes related to the gate stack such as mobility degradation, threshold voltage ( $V_T$ ) instability and oxide breakdown [7]–[10]. These issues need to be characterized under bias conditions relevant for power switching applications, so that the significance for practical applications can be readily assessed.

In this paper, we extensively characterize  $V_{\rm T}$  instabilities during OFF-state stress experiments. Instability refers to any recoverable parametric change in device characteristics during operation as a consequence of dynamic effects associated with traps present in the device structure The stress experiments carried out in this work allow quantifying the cumulative effect on device  $V_{\rm T}$  of OFF-state operating conditions applied for instance in switching converters. Interestingly, the observed  $V_{\rm T}$ increase was found to be positively correlated with increasing drain bias while not being significantly influenced by gate bias, suggesting that the mechanism is related with device epitaxy rather than gate stack. V<sub>T</sub> recovery was assessed at zero bias at different temperatures and a  $\approx$ 1-eV activation energy (*E*<sub>A</sub>) was extracted from the Arrhenius plot of the process. Further characterization was carried out on pseudo-vertical p-n junction diodes – with the same epitaxy as that of the TMOS's – by means of capacitance iso-thermal spectroscopy (C-ITS). These experiments revealed an increase of the depletion capacitance  $(C_{\text{DEP}})$  under reverse bias conditions, accelerated by temperature with the same  $E_A$  as that extracted from the  $V_T$ recovery. This correlation points to trapping effects occurring in the device epitaxy as the mechanism behind both observations.

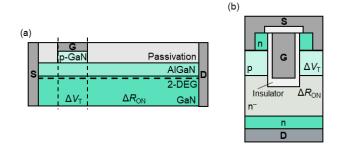

Fig. 1. Schematic representation of (a) lateral p-GaN HEMT and (b) vertical GaN TMOS.

Particularly,  $V_T$  increase during OFF-state stress experiments is attributed to the charging of donor traps in the p-body region by electrons leaking from source to drain under sub-threshold conditions. The observations drawn from experiments were supported by calibrated numerical simulations that reproduced well both  $V_T$  instability and  $C_{\text{DEP}}$  increase when including deep donor traps in the p-type body region with 1-eV ionization energy (with respect to GaN conduction band). Finally, we discuss the possible origin of these epitaxy trap states.

The rest of the paper is structured as follows. Section II gives an overview of reliability aspects of GaN devices, particularly focusing on the comparison between lateral and vertical normally-off transistors. In Sec. III the devices characterized in this work are described. Section IV presents the experimental results. Section V discusses the model proposed to interpret the experiments and the results of the numerical simulations that confirm the interpretation. Section VI draws the conclusions of this work.

## II. LATERAL P-GAN HEMTS VS VERTICAL TRENCH MOSFETS

While lateral GaN devices have already reached commercial maturity [2], [12]–[14], vertical counterparts have started only recently to gather attention from the industry [2]. Fig. 1 schematically depicts a lateral, normally-off, p-GaN/AlGaN/GaN high-electron mobility transistor (HEMT) and a vertical GaN trench MOSFET (TMOS).

The promises of the TMOS are: achieving high breakdown voltages (> 1 kV) without increasing chip area, high  $V_{\rm T}$  values thanks to the inversion-mode operation, lower impact of trapping issues on  $R_{\rm ON}$  compared to lateral GaN devices. The latter point is true provided that the electric field in the OFF-state peaks in the drift region, away from the device surface and gate stack [2]. Nevertheless, owing also to their lower maturity, vertical GaN devices are expected to suffer from charge-trapping related issues. These issues critically affect both conduction and switching losses because of the degradation of key electrical parameters (i.e.,  $V_{\rm T}$  [7],  $R_{\rm ON}$  [15], as well as device capacitances [16]).

In general, trapping mechanisms can be classified depending on: (i) the specific trap parameters determining their dynamics, (ii) the location of the traps within the complex device structure, (iii) the type of carriers being captured/emitted, and (iv) the charging/discharging path of the trap [2].

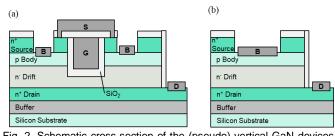

Fig. 2. Schematic cross-section of the (pseudo) vertical GaN devices under study in this work: (a) Trench MOSFET and (b) p-n diode. Devices share the same epitaxy.

| TAB.I. SUMMARY OF MOST RELEVANT $V_{\rm T}$ and $R_{\rm ON}$ instability sources |  |  |

|----------------------------------------------------------------------------------|--|--|

| FOR LATERAL AND VERTICAL GAN DEVICES.                                            |  |  |

|                                       | Lateral p-GaN HEMT                                                                                                                 | Vertical GaN TMOS                                                                                                                         |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| ΔV <sub>T</sub>                       | Hole depletion (p-GaN) [18]<br>Electron/hole trapping<br>(barrier) [19]                                                            | Electron trapping (gate<br>insulator, insulator/GaN<br>interface) [7]<br>Electron trapping<br>(donor traps in p-type<br>body) [This Work] |

| Δ <b>R</b> <sub>on</sub>              | Hole emission (C-doped<br>buffer) [20]<br>Hole virtual gate (barrier) [21]<br>Hot electron trapping<br>(buffer/barrier) [22], [23] | Electron trapping (along trench sidewall) [15]                                                                                            |

| V <sub>G</sub><br>V <sub>GS,MAX</sub> | $t_{M}$                                                                                                                            |                                                                                                                                           |

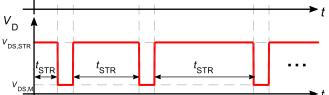

Fig. 3. Sketch of voltage waveforms applied at gate and drain terminals during OFF-state stress experiments (source was kept grounded).  $V_{GS,MAX} = 15 \text{ V}, V_{DS,STR}$  varied between 0 and 40 V  $\Delta V = 10 \text{ V}, V_{DS,M} = 5 \text{ V}. t_{M} = 10 \mu s, t_{STR}$  was increased logarithmically from  $10^{-5}$  to  $10^{2} \text{ s}.$

In practical terms, these aspects need to be considered either for technology optimization or for determining the proper device for the desired application.

Owing to their different topology, GaN lateral and vertical devices are generally affected by different trapping mechanisms, which in turn determine the drift of  $V_{\rm T}$ , and/or  $R_{\rm ON}$ . Tab.I summarizes the most relevant trapping mechanism in both lateral p-GaN HEMT's (i.e., the most common option in commercial applications) and vertical GaN TMOS's (under investigation in this work).

$V_{\rm T}$  instability ( $\Delta V_{\rm T}$ ) is determined by dynamic charge trapping occurring under the gate terminal in lateral devices (p-GaN, AlGaN barrier, GaN buffer) or in either the p-type body region or in the gate insulator in TMOS devices. This occurs because trapped charge affects the capability of the gate terminal to populate the channel – either formed thanks to the two-dimensional electron gas (2-DEG) in HEMT's or to the inversion channel in TMOS's.

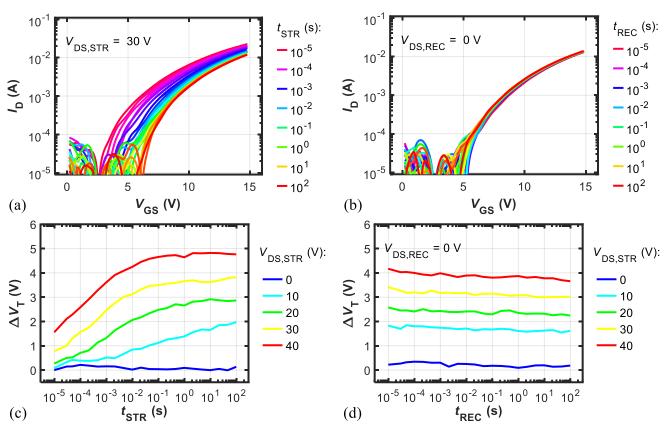

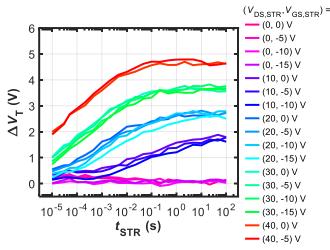

Fig. 4. Analysis of  $V_T$  instability during OFF-state stress by means of fast  $V_T$  transient characterization. Typical  $I_D$ - $V_{GS}$  curves in (a) stress ( $V_{DS,STR} = 30$  V) and (b) recovery ( $V_{DS,REC} = 0$  V) conditions. (c), (d)  $\Delta V_T$  transients extracted during stress and recovery, at different  $V_{DS,STR}$  (see legend).

Depending on the electrical nature of the traps and bias applied to the gate,  $V_{\rm T}$  can shift both negatively and positively [7], [16]–[19].

Dynamic  $R_{ON}$  ( $\Delta R_{ON}$ ) is determined by trapping occurring in the gate-to-drain access region or drift region in lateral and vertical devices, respectively. The two regions in fact are the largest ones in the structure and as such dominate  $R_{ON}$ . Both dynamic  $R_{ON}$  increase and decrease can be observed depending on the operating conditions [20]–[23]. In TMOS's, dynamic  $R_{ON}$  can critically be affected by traps located along the trench sidewalls [15].

#### **III. DEVICE DESCRIPTION**

Devices under test consist of pseudo-vertical GaN Trench MOSFETs on a silicon substrate. The epitaxial stack, obtained by metalorganic chemical vapor deposition (MOCVD) consist of a strain relief buffer layer, an n<sup>+</sup> drain layer (1 µm), an n<sup>-</sup> drift layer (1  $\mu$ m), a p<sup>+</sup> body channel layer (500 nm), and a n<sup>+</sup>-GaN source layer (300 nm). The gate trench was formed with a Clbased inductive coupled plasma reactive ion etching (ICP-RIE) followed by a TMAH wet etching to achieve a vertical sidewall free of the plasma damage. Then, 70 nm silicon di-oxide (SiO<sub>2</sub>) gate dielectric was deposited by low-pressure chemical vapor deposition (LPCVD) at a temperature of 880 °C, followed by a post-deposition annealing at 900 °C, to improve the mobility in the channel [24]. The gate electrode is made out of polysilicon. Drain contacts to the n+ layer are made from the frontside laterally displaced with respect to the TMOS mesa structure creating a pseudo-vertical device.

The structure is a simplified vesion of the classical trench MOSFETs that can nominally operate at low voltages, because of the relatively thin drift layer and the lack of thick bottom dielectric (TBD) [25]–[27], or the p-type shielding [28] usually implemented in other technologies including Si and SiC to optimize the breakdown voltage. The structure of the TMOS's under study is schematically reported in Fig. 2(a). As far as  $V_T$  instability is concerned, performing the analysis on pseudo- or fully-vertical TMOS's does not affect the conclusions of this work, as the device region responsible for the parametric instability is not the drift region but the p-type body region which is the same in both structures.

### IV. DEGRADATION CHARACTERIZATION

We characterized  $V_{\rm T}$  instability after OFF-state stress conditions at different bias and temperatures. We also characterized the deep levels in the semiconductor layers of a p-n diode (fabricated on the same wafer as that of the TMOS's) by means of capacitance isothermal transient spectroscopy (C-ITS) under reverse bias conditions. The latter experiments allowed gaining deeper insights into the mechanism underlying  $V_{\rm T}$  instability.

$V_{\rm T}$  instability characterization was performed under moderate OFF-state stress conditions (i.e.,  $V_{\rm DS,STR} = 0-40$  V,  $\Delta V_{\rm DS} = 10$  V) [29]. Fast  $V_{\rm T}$  transient were acquired as follows: device was stressed at a constant bias ( $V_{\rm DS,STR}$ ) which was periodically interrupted to sample  $V_{\rm T}$  by acquiring  $I_{\rm D}$ - $V_{\rm GS}$  with a fast 10-µs gate voltage ramp, while keeping the drain bias at 5 V.

Fig. 5. Analysis of the OFF-state  $V_{T}$  transients as a function of different  $V_{DS,STR}$  and  $V_{GS,STR}$  (see legend). The increase of  $V_{T}$  is strongly dependent on  $V_{DS,STR}$  and negligibly affected by  $V_{GS,STR}$ .

Fig. 6. Drain and gate leakage current during the step-stress experiment.

$V_{\rm T}$  was defined as the necessary  $V_{\rm GS}$  to have  $I_{\rm D} = 1$  mA. Fig. 3 shows a sketch of the voltage waveforms applied on the gate and drain terminals during these experiments. The same setup was also used to assess recovery, for which  $V_{\rm DS,REC} = 0$  V. Stress and recovery maximum duration was 100 s. All these experiments were carried out at room temperature. To avoid any trapped charge accumulation, devices were exposed to 365 nm (3.4 eV) ultraviolet (UV) illumination for a few minutes between each stress measurement.

The  $I_{\rm D}$ - $V_{\rm GS}$  acquired during stress with  $V_{\rm DS,STR} = 30$  V are reported in Fig. 4(a), from which it can be observed how the stressed devices are subject to a  $V_{\rm T}$  increase, with negligible changes in terms of subthreshold slope and saturation current. The noisy off-state current for  $V_{\rm GS} < 2.5$  V is limited by the inaccuracy of the autozero procedure applied to compensate the current probe offset. Fig. 4(b) shows instead  $I_{\rm D}$ - $V_{\rm GS}$  acquired during recovery after 100-s stress at  $V_{\rm DS,STR} = 30$  V, showing negligible  $\Delta V_{\rm T}$  during the duration of the experiment. The features of  $V_{\rm T}$  instability can be further assessed with the aid Fig. 4(c) and (d), showing  $\Delta V_{\rm T}$  (calculated with respect to the pre-stress value) during stress and recovery, respectively, acquired after different  $V_{\rm DS,STR}$ .

Fig. 7.  $V_{\rm T}$  transients acquired while applying  $V_{\rm DS} = 0$  V after 100-s stress at  $V_{\rm DS,STR} = 30$  V. (Inset) Arrhenius plot extracted from the data.

Fig. 8. C-ITS capacitance transients detected on p-n diodes at different temperatures, while keeping  $V_{\rm R} = -30$  V. Dashed lines are  $C_{\rm DEP}$  fitting curves with stretched exponentials from which the time constants (*r*'s) are obtained. (Inset) Arrhenius plot extracted from the *r*'s.

$\Delta V_{\rm T}$  during stress increases in magnitude (up to saturation) as well as accelerates with increasing  $V_{\rm DS,STR}$ , whereas  $\Delta V_{\rm T}$  during recovery remains flat regardless of  $V_{\rm DS,STR}$ . These results are different from those obtained with gate-stress experiments [29], in which  $V_{\rm T}$  did not show saturation during 1000-s stress and partially recovered in 1000 s.  $V_{\rm T}$  instability during gate-stress experiments were attributed to traps located in the gate oxide near the semiconductor/insulator interface [7], [29]. The different features of  $V_{\rm T}$  instability during OFF-state stress compared to gate stress lead to conclude that it is likely influenced by other mechanisms than oxide traps.

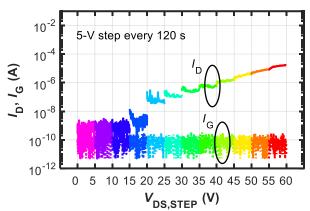

To identify the driving force of the mechanism underlying  $V_{\rm T}$  instability, we performed another set of transient characterization also by applying different  $V_{\rm GS,STR} < 0$  V. This effectively increases  $V_{\rm DG}$  during OFF-state stress. The results of this characterization, along with the different combinations of ( $V_{\rm DS,STR}$ ,  $V_{\rm GS,STR}$ ) are reported in Fig. 5. From Fig. 5 one can observe how  $V_{\rm T}$  increase is strongly affected by drain bias while it is negligibly influenced by gate bias. To understand why this is the case, we acquired drain and gate leakage currents during constant OFF-state stress experiments. These were carried out starting with  $V_{\rm DS} = 0$  V with  $V_{\rm GS} = 0$  V (i.e., below  $V_{\rm T}$ ) for 120 s. After the 120-s period elapsed,  $V_{\rm DS}$  was increased by 5 V and kept constant for another 120 s.

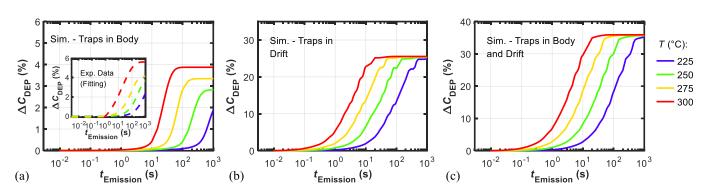

Fig. 9. Simulated C-ITS capacitance transients on p-n diodes at different temperatures, while keeping  $V_R = -30$  V, under different modeling assumptions: traps included in (a) body only, (b) drift only, and (c) both in body and drift regions. Dispersion in case (a) more closely agrees quantitively with experimental data fitting curves corresponding to the part of the transients attributed to carrier emission, reported in the inset for easier comparison.

The process was repeated in a bias range for which catastrophic failure did not occur, i.e., up to  $V_{\rm DS} = 60$  V. The results of this characterization are reported in Fig. 6, which shows that the drain leakage starts to increase at  $V_{\rm DS} = 15$  V, and keeps increasing progressively up to  $V_{\rm DS} = 60$  V. Instead, during the whole bias range gate leakage current stayed approximately constant and below  $\approx 0.1$  nA, indicating good stability of the gate stack.

From all the experimental findings hitherto reported, one then concludes that  $V_{\rm T}$  instability is influenced by electron trapping occurring within deep levels located in the epitaxial structure (rather than in the gate oxide), that get filled by the source-drain leakage current.

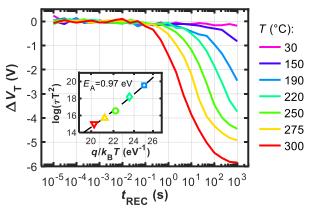

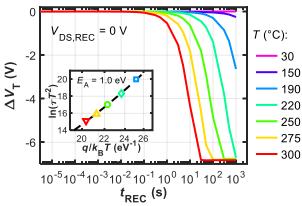

The dynamic properties of the traps responsible for  $V_{\rm T}$  instability were determined by extracting  $V_{\rm T}$  transients at different temperatures. Stress at  $V_{\rm DS,STR} = 30$  V was applied for 100 s, and then  $V_{\rm T}$  evolution was monitored at  $V_{\rm DS} = 0$  V for 1000 s. The results reported in Fig. 7 show that to induce a significant  $V_{\rm T}$  decrease, high temperature (> 150 °C) is required. Furthermore, by fitting  $V_{\rm T}$  decrease with a stretched exponential function following the procedure described in [30], the Arrhenius plot of the process can be built, see inset in Fig. 7. The extracted activation energy ( $E_{\rm A}$ ) is  $\approx 0.97$  eV.

Finally, to confirm that the traps responsible for the  $V_T$  instability are related to the epitaxial structure, we performed an analysis of the deep levels on p-n diodes (on the same wafer as the TMOS's, see Fig. 2(b)) by means of capacitance isothermal transient spectroscopy (C-ITS) [31]. In these structures the absence of the n-type source layer, and thus of the leakage current observed instead in TMOS's, allows to single out the effect of electron emission from traps.

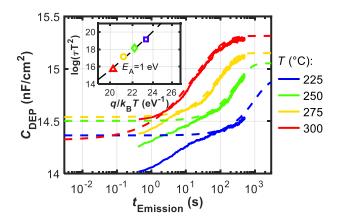

The experimental procedure consists of two phases. First, the diode is biased at a filling voltage  $V_{\rm F} = 0$  V for 100 s, such that any deep levels present in the junction are in a steady-state occupation condition. Then, the diode is reversely biased at  $V_{\rm R} = -30$  V (i.e., the same used to monitor  $V_{\rm T}$  transients) for up to 1000 s and the depletion capacitance ( $C_{\rm DEP}$ ) transient is acquired. In this phase, trapped carriers emitted from traps can be assessed by looking at the variation of  $C_{\rm DEP}$ . Different temperatures were employed to accelerate carrier emission and to obtain an Arrhenius plot as previously. Results are shown in Fig. 8. The data were fitted with stretched exponential curves in the range attributed to carrier emission; the fitting curves are shown in Fig. 8 as dashed lines. The fitting curves were used to

extract the time constants ( $\tau$ 's) to build the Arrhenius plot of the process. The activation energy of the process, obtained from the Arrhenius plot shown in the inset of Fig. 8 is  $\approx 1$  eV, in very close agreement with that obtained from the  $V_T$  transients of Fig. 7. This agreement confirms the hypothesis of traps being located in the epitaxy of the device to be the cause for  $V_T$  instability in TMOS's and  $C_{\text{DEP}}$  increase in p-n diodes.

#### V. NUMERICAL SIMULATIONS

Two-dimensional numerical device simulations were performed with the device simulator included in the Synopsys technology CAD (TCAD) suite [32]. Simulations were devoted to further elucidate the physical mechanism behind both  $V_{\rm T}$ instability and CDEP increase in TMOS's and p-n diodes, respectively. Simulated device cross-sections resemble those of the actual devices, see Fig. 2. The simulation setup for the TMOS is based on the one employed in our previous work [7] where we investigated the role of interface and oxide traps on the sub-threshold slope and the I-V hysteresis, respectively, in similar devices to the ones considered in this work. Driftdiffusion formalism was employed to simulate charge transport. Incomplete ionization of magnesium (Mg) acceptors was taken into account in the p-doped body region. The Mg ionization energy was set to 0.2 eV from the GaN valence band edge. The trap-occupation dynamics was accounted through the Shockley-Read-Hall (SRH) trap-balance equation without any quasi-static approximation. We included deep donor traps in the p-doped body region with 1-eV ionization energy with respect to GaN conduction band edge. The particular choice for location within the epitaxy stems from the modeling of  $C_{\text{DEP}}$ increase in the p-n diodes, explained in the following.

The ionization energy of these traps is set equal to the  $E_A$  extracted from the experiments. Concentration of traps was set to  $N_D = 10^{17}$  cm<sup>-3</sup>. The same bias conditions and timing that were used during characterization (described in Sec. IV.C) were replicated in the simulation setup. Fig. 9 shows the relative  $C_{DEP}$  increase when considering donor traps either (a) in the p-type body, (b) in the n-type drift, and (c) in both regions. As it can be observed, in all cases  $C_{DEP}$  increases over emission time. This happens as a result of the reduction of the depletion layer width on the n-side by the emitted electrons.  $C_{DEP}$  increase is accelerated by temperature, as expected from SRH theory.

Fig. 10. Simulated  $V_{\rm T}$  transients acquired while applying  $V_{\rm DS}$  = 0 V starting from an initial condition with completely filled donors in the p-type region. (Inset) Arrhenius plot extracted from the simulation data.

The  $E_A$  extracted from the Arrhenius plot (not shown) in all cases was 1 eV as expected. However, Fig. 9(a) is the only case for which  $\Delta C_{\text{DEP}}$  quantitatively agrees with experimental observations. For the sake of comparison, the inset in Fig. 9(a) reports  $\Delta C_{\text{DEP}}$  obtained from the fitting curves of experimental data. We assume from now on that traps are located only in the p-type body region.

We simulated the  $V_{\rm T}$  recovery transients in TMOS's corresponding to experiments in Fig. 6, starting from an initial condition with filled donor traps. This condition corresponds to the end of the stress period, during which donor traps are filled by source-drain leakage electrons. In this simulation,  $N_{\rm D} = 3 \times 10^{17}$  cm<sup>-3</sup> to get a quantitative agreement with experiments in terms of magnitude of  $\Delta V_{\rm T}$ . Fig. 10 shows the simulation results, from which one can observe how  $\Delta V_{\rm T}$  is accelerated by temperature with  $E_{\rm A} = 1$  eV (see inset in Fig. 10) which corresponds to the trap ionization energy (given as input to the simulator). This confirms that it is the emission of electrons from donor traps that determines the  $V_{\rm T}$  decrease. As a matter of fact, when emitting electrons, donor traps become positively charged thus reducing the effective p-body doping and decreasing  $V_{\rm T}$  (i.e.,  $\Delta V_{\rm T} < 0$  V).

Generally, having relatively low formation energy, nitrogen vacancies ( $V_N$ ) act as compensating donor impurities in p-type GaN [33]. However,  $V_N$  transition energy is reported to be shallower than 1 eV [33]. Other defects with donor-type behavior and transition energies that can be associated with the 1-eV trap experimentally observed in this work are (defects are ordered from lowest to highest formation energy under p-type growing conditions): nitrogen interstitial ( $N_i$ ); gallium interstitial ( $Ga_i$ ); gallium antisite ( $Ga_N$ ) [33].

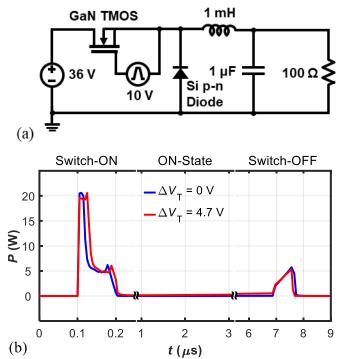

To quantify the ramifications of  $V_T$  instability in a practical scenario, we performed a mixed-mode, circuit/device simulation of a 36-12 V buck converter including the TMOS simulated at the device level.

Voltage and current at transistor terminals are obtained from the self-consistent solution of the circuit and drift-diffusion equations within the external network and within the TMOS itself, respectively. The passive elements of the LC low-pass filter are ideal, as well as the diode except for its forward-bias voltage drop.

Fig. 11. (a) Circuit schematic of the simulated 36-12 V buck converter. (b) Simulated power dissipated by the TMOS during switch-ON, ONstate, and switch-OFF. Switching period is 20  $\mu$ s. The origin on the xaxis corresponds to 3 ms, i.e., after 150 cycles from simulation start to ensure switching regime conditions are reached. The two curves correspond to the fresh TMOS (blue line) and the stressed TMOS with increased V<sub>T</sub> (red curve) of 4.7 V, corresponding to the worst-case as obtained from experimental data in Fig. 4(a).

Fig. 11(a) shows the circuit schematic and (b) the dissipated power by the TMOS during switch-ON, ON-state, and switch-OFF, in steady-state regime for two cases, namely: the unstressed TMOS (i.e.,  $\Delta V_T = 0$  V) and the stressed TMOS with  $\Delta V_T = 4.7$  V corresponding to the worst-case as taken from experimental data in Fig. 4 (a). As it can be seen from Fig. 11,  $V_T$  increase negatively impacts both switching and conduction losses. The increased losses in the buck converter with the degraded TMOS lead to a reduction of the efficiency from about 84% to 78%.

#### **VI.** CONCLUSIONS

We evaluated the threshold voltage instabilities induced by the application of OFF-state bias in vertical GaN Trench MOSFET's.  $V_{\rm T}$  was found to increase during application of the off-state stress bias and recover with a process that is accelerated by temperature with a  $\approx$ 1-eV activation energy ( $E_A$ ). Both drain leakage current and threshold voltage ( $V_{\rm T}$ ) were also found to progressively increase as drain-source stress was increased. Vertical p-n diodes fabricated on the same wafer were also characterized and it was found that the depletion capacitance was also subjected to changes following the application of a reverse bias and accelerated by temperature with the same  $E_A$  as  $V_T$  recovery in TMOS devices. This indicates that the source of these instability is related to traps in the epitaxial layer. These observations were corroborated by numerical simulations showing that including donor traps in the p-type body layer at 1-eV from GaN conduction band edge

allows both  $V_{\rm T}$  and  $C_{\rm DEP}$  instabilities to be reproduced. Specifically,  $V_{\rm T}$  instability in TMOS is determined by the modulation of the effective p-type doping density, while  $C_{\rm DEP}$ increase in the p-n diode is due to the decrease of the effective depletion layer width. The experimental conditions employed in this work are such that the results regarding  $V_{\rm T}$  instability are relevant information for both device engineers as well as application engineers.

#### REFERENCES

- H. Fu, K. Fu, S. Chowdhury, T. Palacios, and Y. Zhao, "Vertical GaN Power Devices: Device Principles and Fabrication Technologies--Part II," *IEEE Transactions on Electron Devices*, vol. 68, no. 7, pp. 3212– 3222, Jul. 2021, doi: 10.1109/TED.2021.3083209.

- [2] M. Meneghini, C. De Santi, I. Abid, M. Buffolo, M. Cioni, R. A. Khadar, L. Nela, N. Zagni, A. Chini, F. Medjdoub, G. Meneghesso, G. Verzellesi, E. Zanoni, and E. Matioli, "GaN-based power devices: Physics, reliability and perspectives," *Journal of Applied Physics*, vol. 130, no. 16, p. 227, 2021, doi: 10.1063/5.0061354.

- [3] F. Jia, X. Ma, L. Yang, X. Zhang, B. Hou, M. Zhang, M. Wu, X. Niu, J. Du, S. Liu, and Y. Hao, "930V and Low-Leakage Current GaN-on-Si Quasi-Vertical PiN Diode With Beveled-Sidewall Treated by Self-Aligned Fluorine Plasma," *IEEE Electron Device Letters*, vol. 43, no. 9, pp. 1400–1403, Sep. 2022, doi: 10.1109/LED.2022.3195263.

- [4] R. Abdul Khadar, C. Liu, L. Zhang, P. Xiang, K. Cheng, and E. Matioli, "820-V GaN-on-Si Quasi-Vertical p-i-n Diodes With BFOM of 2.0 GW/cm2," *IEEE Electron Device Lett.*, vol. 39, no. 3, pp. 401–404, Mar. 2018, doi: 10.1109/LED.2018.2793669.

- [5] Y. Hamdaoui, I. Abid, S. Michler, K. Ziouche, and F. Medjdoub, "Demonstration of avalanche capability in 800 V vertical GaN-on-silicon diodes," *Appl. Phys. Express*, vol. 17, no. 1, p. 016503, Dec. 2023, doi: 10.35848/1882-0786/ad106c.

- [6] J. P. Kozak, R. Zhang, M. Porter, Q. Song, J. Liu, B. Wang, R. Wang, W. Saito, and Y. Zhang, "Stability, Reliability, and Robustness of GaN Power Devices: A Review," *IEEE Trans. Power Electron.*, vol. 38, no. 7, pp. 8442–8471, Jul. 2023, doi: 10.1109/TPEL.2023.3266365.

- [7] N. Zagni, M. Fregolent, A. D. Fiol, D. Favero, F. Bergamin, G. Verzellesi, C. D. Santi, G. Meneghesso, E. Zanoni, C. Huber, M. Meneghini, and P. Pavan, "Physical insights into trapping effects on vertical GaN-on-Si trench MOSFETs from TCAD," *J. Semicond.*, vol. 45, no. 3, pp. 032801–8, 2024, doi: 10.1088/1674-4926/45/3/032501.

- [8] E. Bahat Treidel, O. Hilt, V. Hoffmann, F. Brunner, N. Bickel, A. Thies, K. Tetzner, H. Gargouri, C. Huber, K. Donimirski, and J. Wurfl, "On the Conduction Properties of Vertical GaN n-Channel Trench MISFETs," *IEEE Journal of the Electron Devices Society*, vol. 9, no. February, pp. 215–228, 2021, doi: 10.1109/JEDS.2021.3056697.

- [9] D. Favero, A. Cavaliere, C. De Santi, M. Borga, W. G. Filho, K. Geens, B. Bakeroot, S. Decoutere, G. Meneghesso, E. Zanoni, and M. Meneghini, "High- Temperature PBTI in Trench-Gate Vertical GaN Power MOSFETs: Role of Border and Semiconductor Traps," in 2023 IEEE International Reliability Physics Symposium (IRPS), Mar. 2023, pp. 1–6. doi: 10.1109/IRPS48203.2023.10117667.

- [10] K. Mukherjee, C. De Santi, M. Borga, K. Geens, S. You, B. Bakeroot, S. Decoutere, P. Diehle, S. Hübner, F. Altmann, M. Buffolo, G. Meneghesso, E. Zanoni, and M. Meneghini, "Challenges and Perspectives for Vertical GaN-on-Si Trench MOS Reliability: From Leakage Current Analysis to Gate Stack Optimization," *Materials*, vol. 14, no. 9, Art. no. 9, Jan. 2021, doi: 10.3390/ma14092316.

- [11] J. A. del Alamo and E. S. Lee, "Stability and Reliability of Lateral GaN Power Field-Effect Transistors," *IEEE Transactions on Electron Devices*, vol. 66, no. 11, pp. 4578–4590, Nov. 2019, doi: 10.1109/TED.2019.2931718.

- [12] F. Roccaforte, G. Greco, P. Fiorenza, and F. Iucolano, "An Overview of Normally-Off GaN-Based High Electron Mobility Transistors," *Materials*, vol. 12, no. 10, Art. no. 10, Jan. 2019, doi: 10.3390/ma12101599.

- [13] K. J. Chen, O. Haberlen, A. Lidow, C. L. Tsai, T. Ueda, Y. Uemoto, and Y. Wu, "GaN-on-Si power technology: Devices and applications," *IEEE Transactions on Electron Devices*, vol. 64, no. 3, pp. 779–795, Mar. 2017, doi: 10.1109/TED.2017.2657579.

- [14] G. Iannaccone, C. Sbrana, I. Morelli, and S. Strangio, "Power Electronics Based on Wide-Bandgap Semiconductors: Opportunities and Challenges," *IEEE Access*, vol. 9, pp. 139446–139456, 2021, doi: 10.1109/ACCESS.2021.3118897.

- [15] D. Ji, W. Li, A. Agarwal, S. H. Chan, J. Haller, D. Bisi, M. Labrecque, C. Gupta, B. Cruse, R. Lal, S. Keller, U. K. Mishra, and S. Chowdhury, "Improved Dynamic RON of GaN Vertical Trench MOSFETs (OG-FETs) Using TMAH Wet Etch," *IEEE Electron Device Letters*, vol. 39, no. 7, pp. 1030–1033, Jul. 2018, doi: 10.1109/LED.2018.2843335.

- [16] N. Zagni, M. Fregolent, G. Verzellesi, A. Marcuzzi, C. D. Santi, G. Meneghesso, E. Zanoni, E. B. Treidel, E. Brusaterra, F. Brunner, O. Hilt, M. Meneghini, and P. Pavan, "Correlating Interface and Border Traps With Distinctive Features of C–V Curves in Vertical Al \_\text2 O \_\text3 /GaN MOS Capacitors," *IEEE Transactions on Electron Devices*, pp. 1–6, 2023, doi: 10.1109/TED.2023.3335032.

- [17] A. Stockman, E. Canato, M. Meneghini, G. Meneghesso, P. Moens, and B. Bakeroot, "Schottky Gate Induced Threshold Voltage Instabilities in p-GaN Gate AlGaN/GaN HEMTs," *IEEE Transactions on Device and Materials Reliability*, vol. 21, no. 2, pp. 169–175, Jun. 2021, doi: 10.1109/TDMR.2021.3080585.

- [18] N. Zagni, M. Cioni, M. E. Castagna, M. Moschetti, F. Iucolano, G. Verzellesi, and A. Chini, "Symmetrical V <sub>TH</sub> /R <sub>ON</sub> Drifts Due to Negative/Positive Gate Stress in p-GaN Power HEMTs," in 2022 IEEE 9th Workshop on Wide Bandgap Power Devices & Applications (WiPDA), Redondo Beach, CA, USA, Nov. 2022, pp. 31–34. doi: 10.1109/WiPDA56483.2022.9955267.

- [19] N. Zagni, M. Cioni, A. Chini, F. Iucolano, F. M. Puglisi, P. Pavan, and G. Verzellesi, "Mechanisms Underlying the Bidirectional V<sub>T</sub> Shift After Negative-Bias Temperature Instability Stress in Carbon-Doped Fully Recessed AlGaN/GaN MIS-HEMTs," *IEEE Trans. Electron Devices*, vol. 68, no. 5, pp. 2564–2567, May 2021, doi: 10.1109/TED.2021.3063664.

- [20] N. Zagni, A. Chini, F. M. Puglisi, M. Meneghini, G. Meneghesso, E. Zanoni, P. Pavan, and G. Verzellesi, "'Hole Redistribution' Model Explaining the Thermally Activated *R*<sub>ON</sub> Stress/Recovery Transients in Carbon-Doped AlGaN/GaN Power MIS-HEMTs," *IEEE Trans. Electron Devices*, vol. 68, no. 2, pp. 697–703, Feb. 2021, doi: 10.1109/TED.2020.3045683.

- [21] N. Zagni, G. Verzellesi, A. Bertacchini, M. Borgarino, F. Iucolano, and A. Chini, "Hole Virtual Gate Model Explaining Surface-Related Dynamic RON in p-GaN Power HEMTs," *IEEE Electron Device Letters*, pp. 1–1, 2024, doi: 10.1109/LED.2024.3375912.

- [22] N. Zagni, V. Z. Gao, G. Verzellesi, A. Chini, A. Pantellini, M. Natali, A. Lucibello, L. Latessa, C. Lanzieri, C. D. Santi, M. Meneghini, G. Meneghesso, and E. Zanoni, "Mechanisms of Step-Stress Degradation In Carbon-Doped 0.15 µm Algan/Gan Hemts for Power RF Applications," *IEEE Transactions on Device and Materials Reliability*, pp. 1–1, 2023, doi: 10.1109/TDMR.2023.3305033.

- [23] N. Modolo, C. De Santi, A. Minetto, L. Sayadi, S. Sicre, G. Prechtl, G. Meneghesso, E. Zanoni, and M. Meneghini, "A Physics-Based Approach to Model Hot-Electron Trapping Kinetics in p-GaN HEMTs," *IEEE Electron Device Letters*, vol. 42, no. 5, pp. 673–676, May 2021, doi: 10.1109/LED.2021.3067796.

- [24] M. Henn, C. Huber, D. Scholten, and N. Kaminski, "Effects of the LPCVD Gate Dielectric Deposition Temperature on GaN MOSFET Channels and the Root Causes at the SiO\$\_\text{2}\$-GaN-Interface," *IEEE Trans. Electron Devices*, pp. 1–8, 2024, doi: 10.1109/TED.2023.3347208.

- [25] H. Takaya, J. Morimoto, K. Hamada, T. Yamamoto, J. Sakakibara, Y. Watanabe, and N. Soejima, "A 4H-SiC trench MOSFET with thick bottom oxide for improving characteristics," in 2013 25th International Symposium on Power Semiconductor Devices & IC's (ISPSD), May 2013, pp. 43–46. doi: 10.1109/ISPSD.2013.6694394.

- [26] Y. Zhang, M. Sun, D. Piedra, J. Hu, Z. Liu, Y. Lin, X. Gao, K. Shepard, and T. Palacios, "1200 V GaN vertical fin power field-effect transistors," in 2017 IEEE International Electron Devices Meeting (IEDM), Dec. 2017, p. 9.2.1-9.2.4. doi: 10.1109/IEDM.2017.8268357.

- [27] M. Sun, Y. Zhang, X. Gao, and T. Palacios, "High-Performance GaN Vertical Fin Power Transistors on Bulk GaN Substrates," *IEEE Electron Device Letters*, vol. 38, no. 4, pp. 509–512, Apr. 2017, doi: 10.1109/LED.2017.2670925.

- [28] J. Wei, Z. Wei, H. Fu, J. Cao, T. Wu, J. Sun, X. Zhu, S. Li, L. Zhang, S. Liu, and W. Sun, "Review on the Reliability Mechanisms of SiC Power MOSFETs: A Comparison Between Planar-Gate and Trench-Gate

Structures," *IEEE Transactions on Power Electronics*, vol. 38, no. 7, pp. 8990–9005, Jul. 2023, doi: 10.1109/TPEL.2023.3265864.

- [29] M. Fregolent, A. Del Fiol, C. De Santi, C. Huber, G. Meneghesso, E. Zanoni, and M. Meneghini, "Threshold voltage instability in SiO2-gate semi-vertical GaN trench MOSFETs grown on silicon substrate," *Microelectronics Reliability*, p. 115130, Oct. 2023, doi: 10.1016/j.microrel.2023.115130.

- [30] D. Bisi, M. Meneghini, C. De Santi, A. Chini, M. Dammann, P. Bruckner, M. Mikulla, G. Meneghesso, and E. Zanoni, "Deep-level characterization in GaN HEMTs-Part I: Advantages and limitations of drain current

transient measurements," *IEEE Transactions on Electron Devices*, vol. 60, no. 10, pp. 3166–3175, 2013, doi: 10.1109/TED.2013.2279021.

- [31] M. Fregolent, C. De Santi, M. Buffolo, M. Higashiwaki, G. Meneghesso, E. Zanoni, and M. Meneghini, "Impact of thermal annealing on deep levels in nitrogen-implanted β-Ga2O3 Schottky barrier diodes," *Journal* of Applied Physics, vol. 130, no. 24, p. 245704, Dec. 2021, doi: 10.1063/5.0065434.

- [32] Synopsys, "Sentaurus SDevice Manual (S-2021.06)." 2021.

- [33] J. L. Lyons and C. G. Van De Walle, "Computationally predicted energies and properties of defects in GaN," *npj Comput Mater*, vol. 3, no. 1, p. 12, Mar. 2017, doi: 10.1038/s41524-017-0014-2.