Received 9 January, 2018; revised 11 March, 2018 and 5 April, 2018; accepted 6 April, 2018. Date of current version 31 August 2018. The review of this paper was arranged by Editor N. Collaert.

Digital Object Identifier 10.1109/JEDS.2018.2825360

# Built-In Bias Generation in Anti-Ferroelectric Stacks: Methods and Device Applications

MILAN PEŠIĆ<sup>®</sup><sup>1</sup>, TAIDE LI<sup>1</sup>, VALERIO DI LECCE<sup>2</sup>, MICHAEL HOFFMANN<sup>1</sup>, MONICA MATERANO<sup>1</sup>, CLAUDIA RICHTER<sup>1</sup>, BENJAMIN MAX<sup>1,3</sup>, STEFAN SLESAZECK<sup>1</sup>, UWE SCHROEDER<sup>1</sup>, LUCA LARCHER<sup>2,4</sup>, AND THOMAS MIKOLAJICK<sup>®</sup><sup>1,3</sup>

1 NaMLab gGmbH, 01187 Dresden, Germany 2 MDLSoft, Santa Clara, CA 95054, USA 3 Chair of Nanoelectronic Materials, Technical University of Dresden, 01187 Dresden, Germany 4 DISMI, University of Modena and Reggio Emilia, 42100 Reggio Emilia, Italy CORRESPONDING AUTHOR: M. PEŠIĆ (e-mail: milanpes@gmail.com) This work was supported by the European Fund for regional Development EFRD and the Free State of Saxony, Europe supports Saxony.

**ABSTRACT** The discovery of ferroelectric (FE) properties in binary oxides has enabled CMOS compatible and scalable FE memories. Recently, we reported a simple approach to introduce non-volatility into state-of-the-art dynamic random-access memory stacks that show anti-FE (AFE) behavior. By employing a pair of electrodes with different work functions, a built-in bias is generated. Consequently, this bias modulates the energy potential of the AFE and enables two stable non-volatile states. Using this approach, a significant endurance improvement compared to hafnia-based FE memories can be obtained. In this paper, we investigate the possibility to bypass the usage of asymmetric workfunction electrodes. Using the interface-engineering approach, based on fixed charge or dipole formation, we show two additional methods for built-in bias generation within AFE layer stacks. By characterizing the film properties and performance of AFE capacitors, we compare and investigate retention and endurance of both work function-difference-based and interface-based AFE non-volatile memory. Finally, for the first time we present the concept of a binary oxide-based AFE tunnel junction that leverages both an interface and work function engineered AFE stack.

**INDEX TERMS** Anti-ferroelectric, tunnel-junction, non-volatile memory, DRAM.

#### I. INTRODUCTION

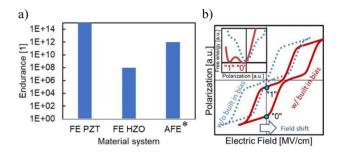

With the growth of the Internet-of-Things (IoT) and the rise of smart cities, the generation of data increases at a tremendous pace [1]. This so-called big data calls for a shift towards memory- or data-centric computing and increases the need for low-power low-latency non-volatile (NV) information storage. Currently, different concepts such as phase change [2], conductive bridge [3], magnetic [4] and ferroelectric (FE) [5]–[7] memories are considered as potential solutions that would guarantee low power, low latency and nonvolatility. Among the listed, FE memories are characterized with unmatchable low writing energy (which is in order of fJ) needed for storing one bit of information [8] accompanied by dynamic random-access memory (DRAM)-like endurance ( $\sim 10^{15}$  stress cycles; see Fig. 1a). State-of-theart FE memories are perovskite based and their scaling has saturated at the 90 nm technology node, limiting them to niche markets [9], [10]. The discovery of ferroelectric properties within the CMOS compatible hafnia-zirconia (HZO) mixtures [11], [12] enabled further scaling of FE memories to 2X nm nodes [6], [13] and beyond. Even though this discovery bridged the scaling gap between state-of-the-art technology nodes and FE memories, the reliability issues in binary oxide based FE memories still need to be fully solved. Due to the high coercive field close to the breakdown field strength, hafnia based FE memories suffer from dielectric breakdown and fatigue, i.e., closure of the memory window (MW). Consequently, the endurance of binary-oxide based FEs is significantly lower compared to state-of-the-art fully-optimized perovskite based FE materials [14]–[16].

Depending on the ratio of hafnia and zirconia in the HZO mixture, a monoclinic, orthorhombic or tetragonal

phase can be stabilized leading to paraelectric, ferroelectric or anti-ferroelectric (AFE) behavior, respectively [12]. Pure ZrO<sub>2</sub> thin films show AFE characteristics. Moreover, this AFE behavior is observed in state-of-the-art ZrO<sub>2</sub> based DRAM capacitor stacks [17], [18]. Analogous to perovskite based FEs [19], [20], ZrO<sub>2</sub> based AFE are characterized with higher endurance strength compared to their FE counterparts [18]. However, in contrast to FEs, AFEs have no remanent polarization at zero field and therefore cannot be used for nonvolatile storage. Recently, Pešić et al. demonstrated that non-volatility can be introduced in AFEs using asymmetric electrodes with different work functions (WF) [17], [18]. Details will be discussed in Section II-B. Using this approach, a significant improvement in the endurance compared to HfO2 based FEs was achieved.

This paper is organized as follows: In the first part, interface and work function based built-in bias generation methods are presented. Afterwards, the device fabrication is described and the physics of the memory effect in biased AFE materials is revisited. Subsequently, the device performance of interface (IF) based and WF based AFE non-volatile memory are compared. Finally, the concept of an anti-ferroelectric tunnel junction, which is characterized by non-destructive read-out (in contrast to 1T-1C AFE-RAM) is presented.

#### II. BUILT-IN BIAS GENERATION

## A. FREE ENERGY ENGINEERING: THEORETICAL ASSESSMENT

In this section, two methods for generation of the built-in bias required for the modification of the energy landscape of the material will be addressed. Before discussing details about the built-in bias generation, basic properties of AFE materials are discussed. Upon the application of an external electric field (higher than the critical field), AFEs exhibit fieldinduced ferroelectricity (FFE) manifested in the constricted polarization-voltage (P-V) hysteresis shown in Fig. 1b) (blue dashed line). With the removal of the electric field excitation, the energy potential (see inset of Fig. 1b) restores its stationary state at P = 0, thus losing its FFE properties. Furthermore, compared to non-volatile FEs, AFEs do not possess a nonzero remanent polarization and hence are cannot be used for non-volatile storage. To enable non-volatility, an introduction of a built-in bias is needed [17], [18]. In the following, two methods for the generation of the built-in bias, required for the modification of the energy landscape of the material, will be discussed.

## B. FREE ENERGY ENGINEERING: WORKFUNCTION APPROACH

The first approach of built-in bias generation is based on asymmetric work function electrodes. Pešić *et al.* [18] reported that sandwiching of the AFE film with different workfunction electrodes generates the desired built-in bias field that can be employed to modify the energy landscape of an AFE capacitor and to enable non-volatile storage in stateof-the-art DRAM stacks (Fig. 1b inset). Consequently, the generated built-in bias field is sufficient to induce a hysteresis shift, and center the left branch of the AFE P-V loop (see Fig. 1b) towards zero-field. Centering of the left branch of the constricted hysteresis loop enables non-volatile switching between the polarized (binary "0") and non-polarized (binary "1") memory state.

The built-in bias field  $E_{built-in}$  generated by using electrodes with different WF values is described by the following equation:

$$E_{built-in} = \frac{1}{t \cdot q} \cdot (WF_{TE} - WF_{BE}), \qquad (1)$$

where *t* represents the thickness of the AFE, *q* is the elementary charge,  $WF_{TE}$  and  $WF_{BE}$  are the workfunction values for the top and bottom electrode, respectively.

**FIGURE 1.** a) Field cycling endurance of a state-of-the-art perovskite capacitor (FE PZT) [8], ferroelectric 1:1 mixture of  $ZrO_2$  and  $HfO_2$  based capacitor (FE HZO) [12] and anti-ferroelectric  $ZrO_2$  based capcaitor (AFE)\* [18]. b) Model of polarization hysteresis of AFE materials at zero external fields with (solid) and without (dotted) built-in bias field. The shift in the polarization characteristics along the field axis results in a  $P_r$  at zero bias and therefore enables non-volatile data storage. Inset denotes corresponding free energy potential (solid) with and (dottet) without built-in bias at zero external field. \*Extrapolated value.

# C. FREE ENERGY ENGINEERING: INTERFACE APPROACH

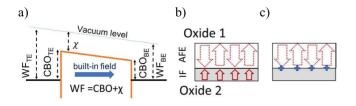

In addition to the asymmetric electrode work function method [17], two additional, interface-based methods were proposed [21]. Here, we suggest that the required built-in bias field can be generated by either introduction of an interfacial dipole [22] (Fig. 2) or fixed charges between two dielectric layers [23]. A surface density difference of oxygen atoms at the interface between two oxide materials can be used as an intrinsic origin for dipole formation [22]. Alternatively, the composition change from one material to another can induce positive or negative fixed charge at the interface [23]. Both effects can be used for introduction of an internal bias field. It should be noted that the direction of the built-in bias field, generated by the asymmetric WFs, can be altered by combining the top electrode (TE) with a higher or lower workfunction material with respect to the bottom electrode (BE). On the other hand, interface charge effects or the dipole orientation can be controlled by the sequence of the deposited layers.

**FIGURE 2.** Built-in bias field generation by a) asymmetric stack comprising electrodes with different work function values and by combining a heterostructure of two oxide materials with different surface density of oxygen which result in either b) dipole formation or c) introduction of fixed charges. CBO and  $\chi$  denote conduction band offset and electron affinity respectively.

### III. FABRICATION STEPS AND CHARACTERIZATION METHODS

### A. METAL-INSULATOR-METAL-STRUCTURES: FABRICATION

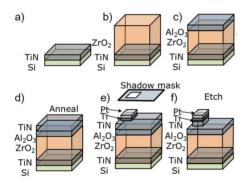

TiN/ZrO<sub>2</sub>/RuO<sub>x</sub> and TiN/ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/TiN metal-insulatormetal (MIM) test structures were deposited on Silicon substrates. The process flow of the TiN/ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/TiN capacitor stack fabrication is given in Fig. 3, whereas the details of the TiN/ZrO<sub>2</sub>/RuO<sub>x</sub> stack fabrication can be found in [18] and [24].

**FIGURE 3.** Process flow used for fabrication of the capacitor stacks under test. a) PVD deposited TIN BE on Si substrate, b) ALD deposited ZrO<sub>2</sub> dielectric, c) ALD deposited Al<sub>2</sub>O<sub>3</sub>, d) PVD deposited TiN top electrode and crystallization anneal, e) PVD deposition of the Ti adhesion layer and Pt hard mask and f) etching of TiN and formation of discrete capacitor structures.

First, a 12-nm thick TiN bottom electrode was deposited by physical vapor deposition (PVD) sputtering at room temperature. After the deposition of the BE, a  $ZrO_2/Al_2O_3$ dielectric stack, with combined thickness of 12 nm, was grown by atomic layer deposition at 230 and 250°C, respectively.  $Al_2O_3$  and  $ZrO_2$  stacks were processed in  $H_2O$ process using trimethylaluminum (TMA), and Zr based metal organic precursor (TEMAZr) as reactants, respectively. To investigate the influence of the thickness of the interfacial  $Al_2O_3$ , the thickness ratio between  $Al_2O_3$  and  $ZrO_2$  was varied, while preserving the total thickness of 12 nm. The dielectric stack was capped by a reactively sputtered 12-nm thick TiN TE. In the following step, the dielectric was crystalized in nitrogen atmosphere by a 20 s rapid thermal anneal at 800 °C. The annealing step of the  $ZrO_2$  film, confined in between two TiN electrodes, results in stabilization of the tetragonal phase (t-phase) which is responsible for the AFE behavior [6], [17], [25]. To prepare the stack for further structuring, circular hard masks consisting of 10 nm Ti (adhesion layer) and 50 nm Pt were deposited in an electron beam evaporator using a shadow mask. Finally, discrete capacitor structures were patterned by wet etching of the TiN in a standard-clean one (SC1) step, thus defining a device area of 9100  $\mu$ m<sup>2</sup>.

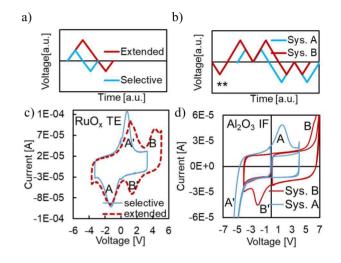

FIGURE 4. Pulse waveform used to obtain the dynamic current of a) WF-engineered AFE capacitor (with indicated extended and selective sweep) and b) IF-engineered equivalent (with indicated left (A) and right (B) system). Comparison of AFE c) TiN/ZrO<sub>2</sub>/RuO<sub>x</sub> and d) TiN/ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/TiN stacks with extended range and selective read-out. Current peak pairs A-A' and B-B' denote left and right system of AFE film, respectivelly. \*I-V characteristics are measured at 1 kHz. \*\*PUND like waveform (b and d) is used to discriminate switching from leakage current.

The above discussed approach should preserve the tetragonal nature and consequent anti-ferroelectric properties of the ZrO<sub>2</sub> based film and generate a built-in bias required for the centering of the left system (switching peak A and A'; see Fig. 4c) of the current-voltage (I-V) curve. Extension of the sweep towards more positive values proves that the TiN/ZrO<sub>2</sub>/RuO<sub>x</sub> stack is still anti-ferroelectric (Fig. 4c dashed trace) but shifted along the voltage axis. Analogous to the WF-engineered case, the IF-based approach results in biasing and centering of the A-A' peak pair around the origin. Introduction of the Al2O3 interfacial layer causes an additional voltage drop and requires the application of a higher voltage that consequently results in a high dynamic leakage current that is comparable to current component originating from switching (see Fig. 4d). On the other side, static current decreases with the increase of the interfacial thickness (see Fig. 5a) indicating the persistence of the interfacial layer. However, a possibility that a portion of the deposited Al<sub>2</sub>O<sub>3</sub> diffuses during anneal cannot be totally excluded. Additional parasitics arising due to the interfacial Al<sub>2</sub>O<sub>3</sub>based dead layer (and its persistence) will be discussed in detail in Section IV-B when addressing the retention of the device.

## **B. CHARACTERIZATION METHODS**

To record the P-V response of the capacitors, an aixACCT TF Analyzer 3000 and Keithley 4200 SCS parameter analyzer were used. Retention and imprint experiments were performed using a semi-automatic probe station from Cascade Microtech and Keithley 4200 SCS parameter analyzer.

#### **IV. COMPARISON OF IF AND WF BASED AFE-RAM**

This section is devoted to the performance investigations of WF and IF engineered AFE memories reflected through the two most important reliability features, i.e., retention and endurance. In addition to benchmarking of these two solutions, engineering guidelines for improvements of these stack are suggested.

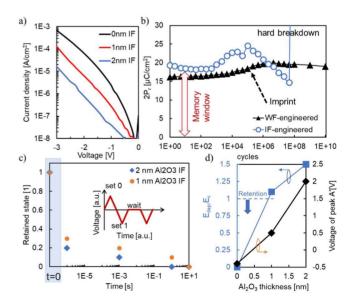

#### A. ENDURANCE

In Fig. 5b), a comparison of the endurance characteristics of WF-engineered and IF-engineered AFE non-volatile memory is shown. WF-engineered AFE memory exhibits a wake-up-free, [16], [26] stable endurance characteristic (see Figure 5) with slight operation induced imprint. It is assumed that the higher-phase uniformity of the film is responsible for the wake-up free behavior [24], [27], while the imprint is caused by asymmetry of electron injection into the device [28]. Compared to the WF-engineered case, the IF-engineered solution requires an increase of the operation voltage due to the voltage drop in the parasitically formed voltage divider comprising active ZrO<sub>2</sub> and dead Al<sub>2</sub>O<sub>3</sub>based layer to achieve polarization values comparable to the WF-based counterparts. In addition, the charging of the ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> interface leads to biasing of the hysteresis and a drop of the remanent polarization. Increased stressing conditions lead to significant leakage, stress induced degradation and premature hard breakdown of the device.

## **B.** RETENTION

Not only is the endurance of the device based on the IFsolution significantly deteriorated, but retention issues could arise as well. In addition to the voltage drop and subsequent increase of the operation voltage, the Al<sub>2</sub>O<sub>3</sub> interface acts as a dead, non-switching layer that will cause a depolarization field [29], [30]. This depolarization field tends to flip the stored memory state and has detrimental impact on the retention of the device. A complete retention test is described by Rodriguez et al. [31] and was applied on AFE RAM in a previous study [27]. In the comprehensive retention study (reported in [27]) we pointed out that the non-polar (positive) state cannot be imprinted or disturbed due to the natural P=0 free energy minimum of the AFE. Hence, here we focus only on the retention of the polar state. The measurement principle is depicted in the inset of Fig. 5c) and it can be understood as follows: After the setting of the negative state, a read-out of the state was performed with sequentially increasing delay; Upon application of the negative set pulse, the current response comprises dielectric (permittivity related) component and switching current components;

Subsequently, a control pulse of the same polarity should contain only a dielectric non-switching component if the polarization state is retained.

As expected with an increase of the thickness of IF layer, retention of the IF-engineered devices is reduced tremendously. Compared to the stable retention performance of the WF-engineered AFE RAM reported in [27], IF-based AFE RAM loses its retention within the first ms already at room temperature. This fast loss of the state can be explained by the increased depolarization field (the values given in Fig. 5d are calculated based on [29] and [30]) and non-significant built-in bias strength of the generated dipole/fixed charge magnitude. In addition to the desired shift of the I-V peaks by formation of the dipole/fixed charges, the IF depolarizes the film and results in higher fields needed for switching of the state. As a result, the distance between the switching peak B and the back-switching peak B' (see Fig. 4d)) increases to such an extent that the peak B' ends up occurring in the negative electric field polarity compared to WF-based solution where all peaks are biased in the same direction. An overview of these dependencies is given in Fig. 5d). Based on these assessments it can be concluded that the WF-based approach would be preferential for the implementation of the AFE non-volatile memory. Nonetheless, engineering of the interface by thinning and the choice of the material that has a higher surface oxygen concentration difference compared to Al<sub>2</sub>O<sub>3</sub> would possibly ensure a dipole large enough to overcome the depolarization fields and modulate the energy potential, thus providing stable retention.

FIGURE 5. Reliability assessment of an AFE memory capacitor stack. a) Static I-V characteristics measured on MIMs with different interface thickness. b) Comparison of endurance of TiN/ZrO<sub>2</sub>/RuO<sub>x</sub>-(black triangles) and TiN/ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/TiN- (empty circles) based AFE RAM. c) Retention of the negative (polar) state measured on IF-engineered (TiN/ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/TiN) AFE capacitor test structures at room temperature. (inset) Waveform used for the assessment of the stored polar state. d) Depolarization field evolution and peak position of current peak A' as function of the thickness of the Al<sub>2</sub>O<sub>3</sub> IF layer.

## **V. ANTI-FERROELECTRIC TUNNEL JUNCTION**

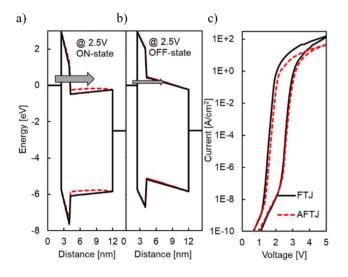

In this last section a combination of the WF-engineered and IF-engineered stack will be discussed for potential memory applications. Similar to the FE counterparts, capacitor based AFE memories can be realized in two flavors, i.e.: a) AFE-RAM characterized with destructive read-out (DRO) and b) AFE tunnel junction (AFTJ) that exhibits non-destructive read-out (NDRO). The concept of the ferroelectric TJ (FTJ) was previously reported in [32]-[35]. Analogous to the FTJ here we suggest that the polarization state of the AFE can be exploited to modulate the band bending and thus the barrier height seen by tunneling electrons, obtaining either a high or a low resistance state (Fig. 6a)). To increase the ON/OFF ratio, a thin interfacial layer equivalent to that discussed in Section III-A can be used [35]. In contrast to FTJ, AFTJ requires a combination of the IF-engineered and WF-engineered device is required. The latter guarantees the non-volatility of the concept while the former assures a respectable magnitude of the tunneling probability and sufficiently high "ON/OFF" margin.

**FIGURE 6.** Band diagram of a simulated ZrO<sub>2</sub>-based AFTJ (solid) compared to HfO<sub>2</sub>-based FTJ (dashed) (with a 1.5-nm substoichiometric Al<sub>2</sub>O<sub>3</sub> interfacial layer) showing the switching mechanism triggered by the polarization reversal in the a) ON (polar) and b) OFF (non-polar) state. c) Simulated I-V curves for 200 × 200 nm<sup>2</sup> (A)FTJ devices. Trap-assisted-tunneling based leakage current is enhanced only at low voltages (<3V), while the switching occurs at higher voltages, where Fowler-Nordheim tunneling dominates. \*It should be noted that simulated structures differ in E<sub>c</sub>, P<sub>r</sub> and P<sub>s</sub> as in the case of FTJ a positive and negative polarization is available compared to only one polar state in AFTJ.

To demonstrate the feasibility of the proposed concept using simulations, a RuO<sub>x</sub>/ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/TiN stack was implemented in commercially available MDLab software. For comparison a FTJ with the same properties and complete  $2P_r$  (double to AFTJ) was simulated. (A)FTJ stack parameters are listed in Table 1 as reported in [24]. To investigate the influence of the AFE material solely on the characteristic of the TJ only  $P_r$  ( $P_s$ ) and  $E_c$  were varied, whereas all remaining parameters of the band diagram were kept constant. Similarly to the interface-engineered AFE-RAM,

TABLE 1. (A)FE tunnel junction simulation parameters.

| Symbol             | Quantity                                         | Value                               |

|--------------------|--------------------------------------------------|-------------------------------------|

| 2P <sub>r</sub>    | Remanent polarization                            | 23.5 (47) μC/cm <sup>2</sup>        |

| $2P_s$             | Saturation polarization                          | $24 (48) \mu C/cm^2$                |

| $E_c$              | Coercive field of AFE (FE)                       | 0.8 (1.2) MV/cm                     |

| $Eg_{ZrO2}$        | Band gap of ZrO <sub>2</sub> (HfO <sub>2</sub> ) | 5.6 eV                              |

| $k_{ZrO2}$         | k-value of ZrO <sub>2</sub> (HfO <sub>2</sub> )  | 30                                  |

| $Eg_{Al2O3}$       | Band gap of $Al_2O_3$                            | 8.7 eV                              |

| $k_{Al2O3}$        | k-value of Al <sub>2</sub> O <sub>3</sub>        | 9                                   |

| $N_t$              | Defect concentration                             | 6.10 <sup>19</sup> cm <sup>-3</sup> |

| $WF_{TiN}$         | TiN workfunction                                 | 4.4 eV                              |

| WF <sub>RuOx</sub> | RuO <sub>x</sub> workfunction                    | 5.2 eV                              |

\*values in parenthesis denote the simulation parameters of the FTJ

Independent on the realization of the active region (AFE vs. FE) OFF state is determined with the defect concentration and trap-assisted-tunneling (TAT) current component and hence stays constant. On the other side, ON state (and its onset) depends on the available polarization that modulates the band diagram in combination with the WF of the electrodes used. Consequently, a slightly higher ON/OFF ratio is observable for the FTJ compared to its AFTJ equivalent. Furthermore, the reduction of the WF of the TE (FTJ case) would results in earlier onset of the Fowler-Northeim and direct tunneling transport component.

#### **VI. CONCLUSION**

After our recent report of an AFE non-volatile memory concept, where asymmetric electrode materials induce a built-in bias field, thus enabling non-volatility in state-of-the art DRAM capacitors, we extend our study and focus on the possibility to bypass the usage of asymmetric work functions. Using the interface-engineering approach, based on fixed charge or dipole formation, we show two additional methods for built-in bias generation within the AFE stack. Based on its endurance and retention performance together with low operation voltages we conclude that the work function approach is more favorable.

Finally, we suggest the concept of a binary-oxide based anti-ferroelectric tunnel junction that combines work function asymmetry, which ensures non-volatility, and interfaceengineering for an increase of the ON/OFF ratio of the memory device. By simulation we investigate the feasibility of the concept that would beside the decrease of the operation voltage enable non-destructive read-out operation.

#### REFERENCES

- [1] "Cisco visual networking index: Forecast and methodology, 2015–2020," San Jose, CA, USA, Cisco, White Paper, Jun. 2016.

- [2] H.-S. P. Wong *et al.*, "Phase change memory," *Proc. IEEE*, vol. 98, no. 12, pp. 2201–2227, Dec. 2010, doi: 10.1109/JPROC.2010.2070050.

- [3] M. Kund *et al.*, "Conductive bridging RAM (CBRAM): An emerging non-volatile memory technology scalable to sub 20nm," in *IEEE Int. Electron Devices Meeting IEDM Tech. Dig.*, Washington, DC, USA, 2005, pp. 754–757, doi: 10.1109/IEDM.2005.1609463.

- [4] K. L. Wang, J. G. Alzate, and P. K. Amiri, "Low-power non-volatile spintronic memory: STT-RAM and beyond," J. Phys. D Appl. Phys., vol. 46, no. 7, 2013, Art. no. 074003.

- [5] J. Müller *et al.*, "Ferroelectric hafnium oxide: A CMOS-compatible and highly scalable approach to future ferroelectric memories," in *Proc. IEEE Int. Electron Devices Meeting*, Washington, DC, USA, 2013, pp. 10.8.1–10.8.4, doi: 10.1109/IEDM.2013.6724605.

- [6] J. Müller et al., "Ferroelectricity in HfO<sub>2</sub> enables nonvolatile data storage in 28 nm HKMG," in Proc. Symp. VLSI Technol. (VLSIT), Honolulu, HI, USA, 2012, pp. 25–26, doi: 10.1109/VLSIT.2012.6242443.

- [7] A. G. Chernikova *et al.*, "Improved ferroelectric switching endurance of La-doped Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> thin films," ACS Appl. Mater. Interfaces, vol. 10, no. 3, pp. 2701–2708, 2017.

- [8] R. Waser, Ed., Nanoelectronics and Information Technology, 3rd ed. Weinheim, Germany: Wiley, May 2012.

- [9] K. Kim and Y. J. Song, "Integration technology for ferroelectric memory devices," *Microelectron. Rel.*, vol. 43, no. 3, pp. 385–398, 2003.

- [10] S. R. Summerfelt *et al.*, "High-density 8Mb 1T-1C ferroelectric random access memory embedded within a low-power 130nm logic process," in *Proc. IEEE Int. Symp. Appl. Ferroelect.*, 2007, pp. 9–10.

- [11] T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, and U. Böttger, "Ferroelectricity in hafnium oxide thin films," *Appl. Phys. Lett.*, vol. 99, no. 10, 2011, Art. no. 102903, doi: 10.1063/1.3634052.

- [12] J. Müller *et al.*, "Ferroelectricity in Simple Binary ZrO<sub>2</sub> and HfO<sub>2</sub>," *Nano Lett.*, vol. 12, no. 8, pp. 4318–4323, 2012, doi: 10.1021/nl302049k.

- [13] M. Trentzsch et al., "A 28nm HKMG super low power embedded NVM technology based on ferroelectric FETs," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2016, pp. 11.5.1–11.5.4, doi: 10.1109/IEDM.2016.7838397.

- [14] M. Pesic *et al.*, "Root cause of degradation in novel HfO<sub>2</sub>based ferroelectric memories," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Pasadena, CA, USA, 2016, pp. MY-3-1–MY-3-5, doi: 10.1109/IRPS.2016.7574619.

- [15] E. Yurchuk *et al.*, "Charge-trapping phenomena in HfO<sub>2</sub>-Based FeFET-type nonvolatile memories," *IEEE Trans. Electron Devices*, vol. 63, no. 9, pp. 3501–3507, Sep. 2016, doi: 10.1109/TED.2016.2588439.

- [16] M. Pešiæ *et al.*, "Physical mechanisms behind the field-cycling behavior of HfO<sub>2</sub>-based ferroelectric capacitors," *Adv. Funct. Mater.*, vol. 26, no. 25, pp. 4601–4612, 2016, doi: 10.1002/adfm.201600590.

- [17] M. Pešić, M. Hoffmann, C. Richter, T. Mikolajick, and U. Schroeder, "Nonvolatile random access memory and energy storage based on antiferroelectric like hysteresis in ZrO<sub>2</sub>," *Adv. Funct. Mater.*, vol. 26, no. 41, pp. 7486–7494, 2016, doi: 10.1002/adfm.201603182.

- [18] M. Pešić et al., "How to make DRAM non-volatile? Antiferroelectrics: A new paradigm for universal memories," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, 2016, pp. 11.6.1–11.6.4, doi: 10.1109/IEDM.2016.7838398.

- [19] X. J. Lou, "Why do antiferroelectrics show higher fatigue resistance than ferroelectrics under bipolar electrical cycling?" *Appl. Phys. Lett.*, vol. 94, no. 7, pp. 2007–2010, 2009.

- [20] L. Zhou, G. Rixecker, A. Zimmermann, and F. Aldinger, "Electric fatigue in antiferroelectric Pb<sub>0.97</sub>La<sub>0.02</sub>(Zr<sub>0.55</sub>Sn<sub>0.33</sub>Ti<sub>0.12</sub>)O<sub>3</sub> ceramics induced by bipolar cycling," *J. Eur. Ceram. Soc.*, vol. 26, no. 6, pp. 883–889, 2006.

- [21] M. Pesic et al., "Anti-ferroelectric ZrO<sub>2</sub>, an enabler for low power nonvolatile 1T-1C and 1T random access memories," in *Proc. 47th Eur. Solid-State Device Res. Conf. (ESSDERC)*, Leuven, Belgium, 2017, pp. 160–163, doi: 10.1109/ESSDERC.2017.8066616.

- [22] K. Kita and A. Toriumi, "Origin of electric dipoles formed at high-k/SiO<sub>2</sub> interface" *Appl. Phys. Lett.*, vol. 94, no. 13, 2009, Art. no. 132902.

- [23] D. K. Simon, P. M. Jordan, T. Mikolajick, and I. Dirnstorfer, "On the control of the fixed charge densities in Al<sub>2</sub>O<sub>3</sub>-based silicon surface passivation schemes," ACS Appl. Mater. Interfaces, vol. 7, no. 51, pp. 28215–28222, 2015, doi: 10.1021/acsami.5b06606.

- [24] M. Pesic, Gate Stack Engineering for Emerging Polarization Based Non-Volatile Memories. Norderstedt, Germany: Books on Demand, 2017.

- [25] M. H. Park *et al.*, "Ferroelectricity and antiferroelectricity of doped thin HfO<sub>2</sub>-based films," *Adv. Mater.*, vol. 27, no. 11, pp. 1811–1831, 2015, doi: 10.1002/adma.201404531.

- [26] E.D. Grimley *et al.*, "Structural changes underlying field-cycling phenomena in ferroelectric HfO<sub>2</sub> thin films," *Adv. Electron. Mater.*, vol. 2, no. 9, 2016, Art. no. 1600173, doi: 10.1002/aelm.201600173.

- [27] M. Pešić et al., "Comparative study of reliability of ferroelectric and anti-ferroelectric memories," *IEEE Trans. Device Mater. Rel.*, to be published.

- [28] M. Pešić et al., "Anti-ferroelectric-like ZrO<sub>2</sub> non-volatile memory: Inducing non-volatility within state-of-the-art DRAM," in Proc. 17th Non-Volatile Memory Technol. Symp. (NVMTS), Aachen, Germany, 2017, pp. 1–4, doi: 10.1109/NVMTS.2017.8171307.

- [29] T. P. Ma and J.-P. Han, "Why is nonvolatile ferroelectric memory fieldeffect transistor still elusive?" *IEEE Electron Device Lett.*, vol. 23, no. 7, pp. 386–388, Jul. 2002.

- [30] U. Schroeder *et al.*, "Impact of field cycling on HfO<sub>2</sub> based nonvolatile memory devices," in *Proc. 46th Eur. Solid-State Device Res. Conf. (ESSDERC)*, Lausanne, Switzerland, 2016, pp. 364–368, doi: 10.1109/ESSDERC.2016.7599662.

- [31] J. Rodriguez et al., "Reliability of ferroelectric random access memory embedded within 130 nm CMOS," in Proc. IEEE Int. Rel. Phys. Symp., 2010, pp. 750–758.

- [32] E. Y. Tsymbal and H. Kohlstedt, "Tunneling across a ferroelectric," *Science*, vol. 313, no. 5784, pp. 181–183, 2006.

- [33] H. Kohlstedt, N. A. Pertsev, J. R. Contreras, and R. Waser, "Theoretical current-voltage characteristics of ferroelectric tunnel junctions," *Phys. Rev. B, Condens. Matter*, vol. 72, no. 12, 2005, Art. no. 125341.

- [34] A. Gruverman *et al.*, "Tunneling electroresistance effect in ferroelectric tunnel junctions at the nanoscale," *Nano Lett.*, vol. 9, no. 10, pp. 3539–3543, 2009.

- [35] S. Fujii *et al.*, "First demonstration and performance improvement of ferroelectric HfO<sub>2</sub>-based resistive switch with low operation current and intrinsic diode property," in *Proc. IEEE Symp. VLSI Technol.*, 2016, pp. 1–2.

**MILAN PEŠIĆ** received the Ph.D. degree from the Technical University of Dresden, Germany, in 2017. His research activities are in the field of emerging nonvolatile memories and devices. Particularly, his interests are the high-k devices, ferroelectrics, electrical characterization and modeling of emerging NVMs as well as the energy efficient electronics (steep-slope device). In 2018, he joined MDLSoft Inc., a Silicon Valley company developing software solutions for the simulation of micro/nano-electronic devices and Ferroelectric Memory Company developing ferroelectric memories. He was with NaMLab, Dresden, Germany. He has authored and co-authored over 30 technical papers and patent.

**TAIDE LI** received the M.Sc. degree in nanoelectronic systems from TU Dresden in 2017.

**VALERIO DI LECCE** received the M.Sc. degree in electronic engineering and the Ph.D. degree in electronics and telecommunication engineering from the University of Modena and Reggio Emilia, Modena, Italy, in 2008 and 2012, respectively. From 2012 to 2016, he was a Post-Doctoral Research Fellow with the E. De Castro Advanced Research Center on Electronic Systems, University of Bologna, Bologna, Italy. He is currently a Software Developer with MDLab. **MICHAEL HOFFMANN** received the B.Sc. degree in electrical engineering and information technology from Otto-von-Guericke University, Magdeburg, Germany, in 2013 and the M.Sc. degree in electrical engineering from TU Dresden, Germany, in 2016. He is currently pursuing the Ph.D. degree with NaMLab gGmbH, Dresden, Germany. In 2016, he was a visiting student researcher with the University of California at Berkeley, USA, for six months. His research interests include nanoelectronic devices and materials for ultralow power computing as well as energy conversion and storage. In particular, his current research is focused on negative capacitance in HfO<sub>2</sub> and ZrO<sub>2</sub> based ferroelectric materials for steep slope electronic devices.

**MONICA MATERANO** received the B.Sc. degree from the Faculty of Materials and Nanotechnology Engineering, Politecnico di Milano and the M.Sc. degree in nanoscience and nanotechnology within the Erasmus Mundus Program which involved KU Leuven and TU Dresden Universities in 2017. She is currently pursuing the Ph.D. degree with NaMLab Institute, Dresden. The focus of her work is fabrication and characterization of ferroelectric capacitors for memory applications.

**CLAUDIA RICHTER** received the Dipl.Ing. (FH) degree in physical engineering from the University of Applied Science Wildau, Germany, in 2010. Since 2011, she has been with NaMLab gGmbH, Germany. Her research activities are in field of atomic layer deposition and thin film characterization. In particular, her work focuses on the development of the new ferroelectric hafnium oxide thin films.

**BENJAMIN MAX** received the Diploma degree in physics from Otto-von-Guericke University, Magdeburg, in 2014. He is currently pursuing the Ph.D. degree with the Chair for Nanoelectronic Materials in cooperation with NaMLab gGmbH, Technische Universität Dresden. His research activities are in the field of resistive and ferroelectric switching properties of hafnium oxide as well as in the area of ferroelectric tunnel junctions.

**STEFAN SLESAZECK** received the Ph.D. degree from TU Dresden. He is a Senior Scientist with NaMLab responsible for concept evaluation, hardware development, electrical characterization, and modeling of memories. One of his research interests is the development of novel computing paradigms based on memristors. He was a Project Leader for the predevelopment of new memory concepts with Qimonda, Dresden, Germany, focusing on concept evaluation for 1T-DRAM, including floating body devices, cell concepts, and access schemes for WL-driver and sense amplifier. As a Device Engineer with Infineon Technologies, he focused on the module development of 3-D DRAM access devices in 65 and 46 nm buried word line technology and predevelopment of 3-D DRAM access devices as FinFET and EUD. **UWE SCHROEDER** received the Doctoral degree from the University of Bonn, Germany, including a research visit with UC Berkeley. He was a Post-Doctoral Researcher with the University of Chicago. He joined Infineon (formerly Siemens) Semiconductor in 1997 for capacitor development in the DRAM Development Alliance with IBM, before transferring to Infineon's Memory Development Center, Dresden, Germany, in 2000, where he continued the research on high-*k* dielectrics and their integration into DRAM capacitors. During this time the ferroelectric properties of Hf02-based dielectrics were found. In 2009, he moved to NaMLab and pursued his work on high-*k* dielectrics and ferroelectric Hf02-layers.

LUCA LARCHER received the Ph.D. degree in information engineering from the University of Modena and Reggio Emilia in 2002, where he is currently a Professor of electronics. His main research interests include the modeling and characterization of nonvolatile memory devices and of physical mechanisms governing the charge transport and degradation in high-k dielectrics. In this area, he has worked on either classical flash memory devices and innovative NVM technologies, such as charge trapping memory devices (NROM, SONOS, and TANOS), PCM and RRAM devices. In 2013, he co-founded a start-up company developing novel software solution for the simulation of emerging electron devices, such as RRAM. He is also active in the characterization and design of integrated circuits for both communications and energy harvesting applications in CMOS technology. He has authored and co-authored a book and a chapter in a book, and over 200 technical papers published on international journals and proceedings of international conferences. He has joined the technical and executive committees of the IEDM, IRPS, ESREF, DATE, and IIRW.

**THOMAS MIKOLAJICK** received the Diploma (Dipl.-Ing.) degree in electrical engineering and the Ph.D. degree in electrical engineering from the University Erlangen-Nuremberg in 1990 and 1996, respectively. From 1996 to 2006, he was in the semiconductor industry developing CMOS processes, ferroelectric memories, emerging nonvolatile memories and flash memories first at Siemens Semiconductor and later at Infineon. In 2006, he moved back to academia taking over a professorship for material science of electron devices and sensors at the University of Technology Freiberg. In 2009, he joined Technische Universität Dresden, where he currently holds a professorship for nanoelectronic materials in combination with the position of Scientific Director with NaMLab GmbH. He has authored or co-authored over 350 publications in scientific journals or at scientific conferences and inventor or co-inventor of about 50 patents.