# Understanding the Excess 1/f Noise in MOSFETs at Cryogenic Temperatures

Ruben Asanovski<sup>®</sup>, *Graduate Student Member, IEEE*, Alexander Grill<sup>®</sup>, *Member, IEEE*, Jacopo Franco<sup>®</sup>, *Member, IEEE*, Pierpaolo Palestri<sup>®</sup>, *Senior Member, IEEE*, Arnout Beckers<sup>®</sup>, Ben Kaczer, and Luca Selmi<sup>®</sup>, *Fellow, IEEE*

Abstract—Characterization, modeling, and development of cryo-temperature CMOS technologies (cryo-CMOS) have significantly progressed to help overcome the interconnection bottleneck between qubits and the readout interface in quantum computers. Nevertheless, available compact models still fail to predict the deviation of 1/f noise from the expected linear scaling with temperature (T), referred to as "excess 1/f noise," observed at cryogenic temperatures. In addition, 1/f noise represents one of the main limiting factors for the decoherence time of qubits. In this article, we extensively characterize low-frequency noise on commercial 28-nm CMOS and on research-grade Ge-channel MOSFETs at temperatures ranging from 370 K down to 4 K. Our investigations exclude electron heating and bulk dielectric defects as possible causes of the excess 1/f noise at low temperatures. We show further evidence for a strong correlation between the excess 1/f noise and the saturation of the subthreshold swing (SS) observed at low temperatures. The most plausible cause of the excess noise is found in band tail states in the channel acting as additional capture/emission centers at cryogenic temperatures.

*Index Terms*—1/f noise, cryo-CMOS, MOSFET, quantum computing, traps.

#### I. INTRODUCTION

UANTUM computers represent a promising disruptive technology able to solve algorithms that are computationally unfeasible on classical computers (e.g., prime number factorization) [1]. Implementing a system with thousands of logical qubits would greatly advance fields such as cryptography, artificial intelligence, and physics simulations [2], [3],

Manuscript received 17 November 2022; revised 23 December 2022; accepted 29 December 2022. Date of publication 6 January 2023; date of current version 24 March 2023. This work was supported in part by imec's Industrial Affiliation Program on Quantum Computing and Cryoelectronics and in part by the "Università degli Studi di Modena e Reggio Emilia" through the "Bando giovani ricercatori 2021." This article is an extended version of a paper presented at IEDM 2022. The review of this article was arranged by Editor G. Meneghesso. (Corresponding author: Ruben Asanovski.)

Ruben Asanovski and Luca Selmi are with the Dipartimento di Ingegneria Enzo Ferrari, Università degli Studi di Modena e Reggio Emilia, 41121 Modena, Italy (e-mail: ruben.asanovski@unimore.it).

Alexander Grill, Jacopo Franco, Arnout Beckers, and Ben Kaczer are with imec, 3001 Leuven, Belgium.

Pierpaolo Palestri is with the Dipartimento Politecnico di Ingegneria e Architettura, Università degli Studi di Udine, 33100 Udine, Italy.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2022.3233551.

Digital Object Identifier 10.1109/TED.2022.3233551

[4]. In most applications, the qubits operate at temperatures of a few mK, while the control electronics are placed outside the cryostat and operate at room temperature. In such an implementation, long wires between qubits and the control electronics increase the latency, noise, and complexity of the system. Wiring is thus a major bottleneck in realizing quantum computers with many qubits [5]. Significant improvements could be obtained by placing the qubit control electronics in a chamber at 4 K next to the quantum processor. CMOS technology is the preferred candidate for this task due to its excellent performance, availability, and low cost [6]. However, requirements for controlling numerous qubits are stringent, especially in terms of power consumption and noise [7]. Several cryo-CMOS qubit controllers have been demonstrated [8], yet more accurate noise characterization and modeling at low temperatures are needed to further improve their performance. Moreover, 1/f noise is one of the limiting factors for the decoherence time of qubits [9], [10]. Identifying the origin of the 1/f noise at cryogenic temperatures in MOSFETs could eventually lead to improved decoherence times in qubits. A better understanding of the 1/f noise at low temperatures is thus fundamental for both cryo-CMOS and qubits.

Based on carrier number fluctuations (CNFs) with correlated mobility fluctuations (MFs) [11], the expression for the inputreferred 1/f drain current noise ( $S_{vg} = S_{id}/g_m^2$ ) is

$$S_{\rm vg} = \frac{qkTN_{\rm BT}}{WLC_{\rm ox}^2\alpha} \cdot \frac{1}{f} \cdot \left(1 + \Omega \frac{I_D}{g_m}\right)^2 \tag{1}$$

where  $N_{\text{BT}}$  is the volumetric gate dielectric trap density per unit energy,  $g_m$  is the transconductance,  $I_D$  is the drain current,  $C_{\text{ox}}$  is the gate capacitance per unit area, f is the frequency,  $\alpha$  is the exponent of wentzel-kramers-brillouin (WKB) tunneling probability for a rectangular barrier,  $\Omega$  is a parameter related to MF, and W and L are the width and length of the channel, respectively. Equation (1) predicts a linear temperature scaling when CNF dominate ( $\Omega I_D/g_m \ll 1$ ), while noise measurements on a single device [12], [13] and the noise figure of circuits operating at 4 K [8] show that the noise is significantly higher than this prediction. Currently, the behavior of 1/f noise at low temperatures is not explained by any available 1/f noise model. Moreover, there is a lack of extensive noise characterization data at cryogenic temperatures needed to develop dependable and accurate noise models.

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

In this article, we measure commercial 28-nm CMOS devices and research-grade Ge MOSFETs down to cryogenic temperatures, and we critically analyze many possible causes of this excess noise at low temperatures. The article proceeds as follows. Section II introduces the experimental setup and the measurement conditions, while Section III presents the experimental results and discussion. Finally, Section IV summarizes the main outcomes.

# **II. EXPERIMENTAL SETUP**

DC and noise measurements from 370 K down to 4 K were performed with a Lakeshore CRX-4 K cryogenic probe station and a Keysight E4727A noise analyzer.

We measured foundry 28-nm bulk MOSFETs with ultralow  $V_T$  and different areas. Ge-channel MOSFETs with  $W = 10 \ \mu \text{m}$  and  $L = 1 \ \mu \text{m}$  fabricated at imec [14] extend the analysis to alternative channel materials.

Great care has been taken to ensure a stable temperature during the noise characterization and to avoid any drift of the contact resistance. The same gate voltage overdrive  $(V_{ov} = V_{gs} - V_T)$ , where  $V_T$  is extrapolated from the linear  $I_D - V_{gs}$  curve at the point of maximum  $g_m$  [15]) was kept across different temperatures when measuring noise above the threshold to maintain the same inversion condition. On the other hand, we kept the same drain current when measuring in the subthreshold.

#### **III. RESULTS AND DISCUSSION**

In this section, we first present the DC, AC, and noise characterization across temperatures of the devices introduced in Section II. After that, we extensively discuss possible causes of excess 1/f noise. Finally, we investigate the correlation between 1/f noise and band tail states.

#### A. DC and AC Characterization

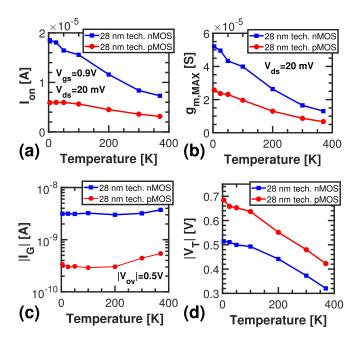

The transfer characteristics, transconductance, and gate capacitance of MOSFETs in 28-nm technology with  $W = 1 \ \mu \text{m}$  and  $L = 0.5 \ \mu \text{m}$  from 370 K down to 4 K have been reported in [16]. Fig. 1 shows the temperature trends of  $I_{\text{on}}$  (defined as  $I_D$  at  $V_{\text{gs}} = 0.9$  V and  $V_{\text{ds}} = 20$  mV),  $g_{m,\text{MAX}}$ ,  $|I_G|$ , and  $|V_T|$ . The  $I_{\text{ON}}$  current and the maximum transconductance  $g_{m,\text{MAX}}$  increase at decreasing temperatures, while Fig. 1(c) shows that  $|I_G|$  is essentially unvaried with T. The  $|V_T|$  increases by approximately 150–200 mV when going from 300 to 4 K. As shown in [16], the gate capacitance of these devices does not vary when going from 295 K down to 4 K. Therefore, the value of  $C_{\text{ox}}$  does not introduce any additional temperature dependence in the  $S_{\text{vg}}$  [see (1)].

## B. Temperature Scaling of 1/f Noise

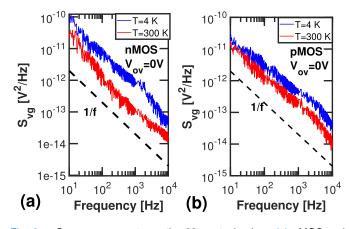

To analyze how the noise scales with temperature, we fit  $S_{vg}$  measured at  $V_{ds} = 20$  mV with a dedicated 1/f curve for each temperature; this is motivated by the fact that low-frequency noise in large-area devices exhibits an essentially 1/f dependence in the explored frequency range (10 Hz to 10 kHz). In the CNF model,  $S_{vg} \cdot f$  has no dependence on  $I_D$ , while in

Fig. 1. Plot of (a)  $I_{on}$ , (b)  $g_{m,MAX}$ , (c)  $|I_G|$ , and (d)  $|V_T|$  against temperature for the 28-nm technology nMOS and pMOS.

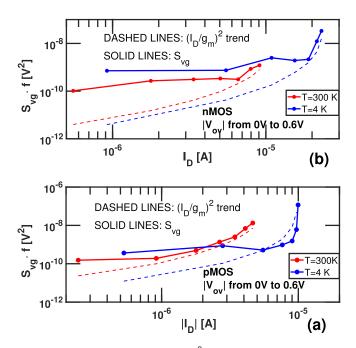

Fig. 2. Plot of  $S_{vg} \cdot f$  (solid) and  $(I_D/g_m)^2$  trend (dashed) as a function of  $I_D$  for the 28-nm technology (a) nMOS and (b) pMOS at T = 300 K and T = 4 K. Each point corresponds to a  $|V_{ov}|$  that goes from 0 to 0.6 V with a 0.1 V step. At low  $I_D$  (low  $V_{ov}$ ), CNFs dominate the noise, while MFs dominate at high  $I_D$  (high  $V_{ov}$ ); see (1).

the MF model it has a  $(I_D/g_m)^2$  dependence [see (1)]. Fig. 2 shows  $S_{vg} \cdot f$  versus  $I_D$  for T = 300 K and T = 4 K, and for  $|V_{ov}|$  ranging from 0 to 0.6 V with a 0.1 V step (both nMOS and pMOS). As one can see, at low  $I_D$  (small  $V_{ov}$ ) CNF describe the noise better, especially in the nMOS, while at high  $I_D$  (large  $V_{ov}$ ), MF dominate. Notice that the dominant mechanism (CNF or MF) for a given  $V_{ov}$  is the same at T = 300 K and T = 4 K.

Fig. 3.  $S_{vg}$  measurements on the 28-nm technology (a) nMOS and (b) pMOS at 300 and 4 K for  $V_{ov} = 0$  V and  $V_{ds} = 20$  mV. Notice that the noise amplitude at 4 K is higher than the one at 300 K, contradicting the linear temperature dependence of (1).

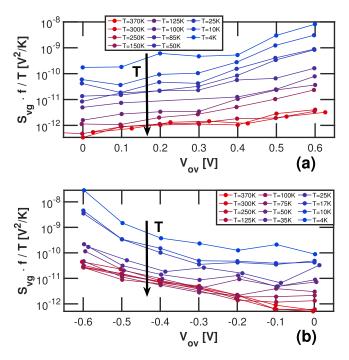

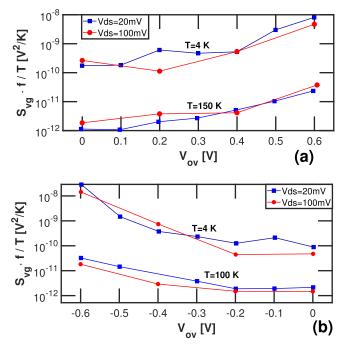

Fig. 4. Plot of  $S_{vg} \cdot f/T$  as a function of  $V_{ov}$  for the 28-nm technology (a) nMOS and (b) pMOS at different temperatures and  $V_{ds} = 20$  mV. Notice that  $S_{vg} \cdot f/T$  increases at decreasing temperatures, contrary to the prediction of (1).

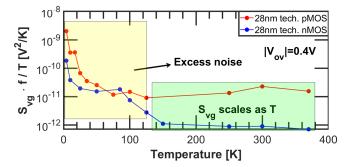

Fig. 3 compares  $S_{vg}$  measured at 300 and 4 K on the 28-nm technology MOSFETs at  $V_{ov} = 0$  V where CNF dominate. The noise at 4 K is higher than at 300 K; therefore,  $S_{vg}$  does not scale linearly with *T* as predicted by the commonly used model of (1). We examine the temperature dependence of  $S_{vg}$  at different  $V_{ov}$  for a more comprehensive analysis. If the 1/f noise scales with *T*, one should obtain the same value of  $S_{vg} \cdot f/T$  across different temperatures for a given  $V_{ov}$ . Fig. 4 reveals clearly that at low temperatures, the curves do not longer overlap (as they instead do at temperatures above 100 K) for neither n- and p-MOSFETs, and an excess 1/f noise of approximately two orders of magnitude appears at 4 K compared to room temperature. In addition, the excess

Fig. 5. Plot of  $S_{vg} \cdot f/T$  versus temperature at  $|V_{ov}| = 0.4$  V for the 28-nm technology nMOS and pMOS.  $S_{vg}$  scales as T [in accordance with (1)] down to approximately 100 K. Below that, the  $S_{vg}$  has an unexpected increase.

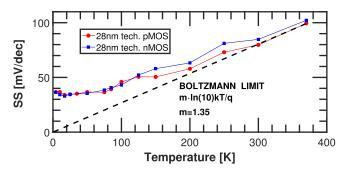

Fig. 6. Comparison between the SS extracted at  $I_D \approx 10$  nA for the 28-nm technology nMOS and pMOS with  $W = 1 \ \mu$ m and  $L = 0.5 \ \mu$ m at different temperatures and the Boltzmann limit. We found that the SS starts saturating around T = 100 K.

noise observed in Fig. 4 is present for all the  $V_{ov}$  values, indicating that the excess 1/f noise shows up in both CNF and MF regimes. Therefore, the excess noise is independent of the noise mechanism (CNF or MF) dominating the 1/f noise.

Focusing the analysis on  $|V_{ov}| = 0.4$  V in Fig. 5, we see that the noise scales with *T* down to approximately 100 K. Below that *T*, there is a significant increase not predicted by (1). Notice that the subthreshold swing (SS) saturates around 100 K as well (Fig. 6), consistently with [17], suggesting a strong correlation between this phenomenon and the excess 1/f noise.

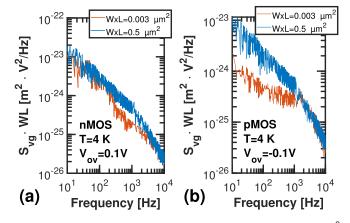

Fig. 7 confirms the area scaling of the noise amplitude at 4 K by plotting  $S_{vg} \cdot WL$  of devices with different areas at  $|V_{ov}| = 0.1$  V. The  $S_{vg} \cdot WL$  partly overlap, suggesting that the same defects are contributing to the noise. The  $S_{vg}$  of small-area devices is missing some noise contributions when compared to  $S_{vg}$  of large-area devices as the number of defects in each device starts to become countable.

## C. Investigating the Origin of the Excess Noise

Several physical mechanisms are possible candidates to explain this excess 1/f noise. Since this effect is observed on a single-channel device in the linear region with low dissipated power ( $P_{\text{diss}} \leq 3 \ \mu\text{W}$ ), self-heating can be safely excluded [18].

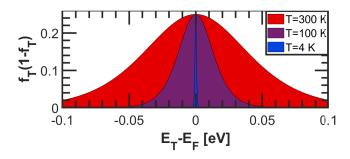

The linear *T*-scaling of (1) originates from the integral  $\int_{-\infty}^{+\infty} f_T (1 - f_T) dE_T$  [19], where  $f_T$  is the near-equilibrium

Fig. 7. Comparison between  $S_{vg} \cdot WL$  of a large-area ( $WL = 0.5 \ \mu m^2$ ) and small-area ( $WL = 0.003 \ \mu m^2$ ) (a) nMOS and (b) pMOS at  $T = 4 \ K$  and  $|V_{ov}| = 0.1 \ V$ .

Fig. 8. Plot of  $f_T(1 - f_T)$  versus  $E_T - E_F$  for different temperatures. The colored area under the curves represents the integral and is equal to kT.

occupation function of the dielectric traps. Assuming that  $f_T$ is described by a Fermi function with Fermi level  $E_F$ , the integral above is the area under a bell-shaped function centered at  $E_T = E_F$  (Fig. 8). The value of this integral is at most equal to kT but never larger than that. Therefore, it cannot predict the excess noise observed in Figs. 3-5. However, notice that the T going into  $f_T$  represents the *electron* temperature, which can be higher than the *lattice* and *ambient* temperatures as electrons gain kinetic energy drifting along the channel. To check whether the electron temperature plays a role in the observed phenomenon, we remeasured the same curves of Fig. 4 with an increased  $V_{ds}$  of 100 mV instead of the previously used  $V_{ds}$  of 20 mV. This voltage range maintains the FET in the linear region [as required by (1)] while increasing the lateral electric field in the channel and hence the average electron energy. As seen in Fig. 9, the  $S_{vg} \cdot f/T$  scaling with temperature (for a fixed  $V_{ov}$ ) is essentially independent of  $V_{ds}$ . Therefore, we can also rule out electron heating as the main cause behind the excess noise.

At low temperatures, the energy alignment between the channel Fermi level and dielectric traps could be different compared to room temperature, even at the same  $V_{ov}$ . If the dielectric trap distribution in energy is very narrow, a slight change in the energy alignment could increase  $N_{BT}$  seen in (1) and explain the excess 1/f noise. However, such a huge  $N_{BT}$  change would likely increase trap-assisted tunneling (TAT) and, therefore, the gate leakage current [20]. As shown in [16]

Fig. 9. Plot of  $S_{vg} \cdot f/T$  versus  $V_{ov}$  for the 28-nm technology (a) nMOS and (b) pMOS at different  $V_{ds}$  and two different temperatures. The  $S_{vg}$  does not increase even if  $V_{ds}$  is increased by a factor of 5, ruling out electron heating as the main cause of excess noise.

and Fig. 1(c),  $I_G$  does not increase at low temperatures (it even slightly decreases for the pMOS). Furthermore, pMOS and nMOS are sensitive to different dielectric defect energies [21], [22]; hence, if the excess noise were related to  $N_{\rm BT}$ , it would likely show different signatures for the two device types. However, we do not see any notable difference between the temperature noise scaling of nMOS and pMOS in Fig. 5. Therefore, we conclude that the excess noise cannot be attributed to an increased density of active traps in the bulk of the dielectric at low temperatures.

Incomplete ionization of the bulk doping could also induce additional fluctuations in the drain current at low temperatures. However, the foundry 28-nm pMOS and nMOS feature different bulk doping concentrations [23]. In particular, the nMOS channel doping concentration is one order of magnitude higher than the pMOS one, while we do not see this remarkable asymmetry in the excess noise behavior of Fig. 5. We can thus rule out incomplete ionization of bulk doping as the main source of 1/f excess noise.

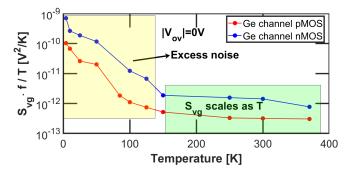

To check whether the excess 1/f noise is related to the channel material, we repeat the noise measurements of Fig. 4 on Ge-channel MOSFETs. Fig. 10 shows that the excess noise appears at a similar temperature also in Ge MOSFETs. Consequently, the excess 1/f noise is not related to a particular channel material.

# D. Relationship Between Band Tail States and 1/f Noise

As stated above, both the excess 1/f noise and the saturation of SS appear below 100 K. SS saturation is attributed to disorder-induced states (i.e., states created by interrupted crystalline periodicity, surface roughness, impurities, strain, etc.)

Fig. 10. Plot of  $S_{vg} \cdot f/T$  versus temperature at  $|V_{ov}| = 0$  V for Ge-channel nMOS and pMOS.  $S_{vg}$  scales as T [in accordance with (1)] down to approximately 100 K. After that,  $S_{vg}$  has an unexpected increase (similar to Fig. 5) even with Ge as channel material.

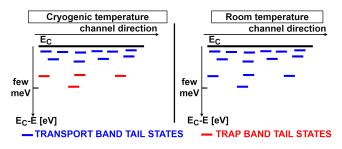

Fig. 11. Sketch of band tail states along the channel direction at cryogenic and room temperature.

with energies close to the conduction/valence bands of the channel. These so-called band tail states are often modeled with an exponentially decaying distribution in energy [17]. To comply with the observed trends of Figs. 5 and 10, the amount of band tail states that act as traps would need to increase at cryogenic temperatures. As sketched in Fig. 11, our measurements suggest that band tail states start to behave as traps at cryogenic temperatures. The definition adopted to distinguish "transport" and "trap" states is based on their occupation kinetics. Thus, a state is a trap if its occupancy fluctuates with a frequency low enough to be inside the noise measurement window (in our case 10 Hz-10 kHz). This behavior could be related to the temperature dependence of the hopping mechanism in band tail states [24]. The relationship between band tail states and excess noise is also suggested by [12] where a correlation is observed between SS saturation and an increase in 1/f noise at low T by varying the surface crystal orientation (hence, the surface density of Si atoms and thus of band tail states).

To check if these states can be responsible for the 1/f noise at cryogenic temperatures, we calculate  $S_{vg}$  for the CNF region according to the following expression [25], [26]:

$$S_{\rm vg} = \frac{q^2}{WLC_{\rm ox}^2} \iint \frac{4f_T(1-f_T)\tau}{1+(2\pi f\,\tau)^2} N_{\rm BT}K(z) \ dE_T dz \quad (2)$$

where z is the direction perpendicular to the channel and  $\tau$  is the trapping/de-trapping time implemented according to the nonradiative multiphonon (NMP) model with correction for cryogenic temperatures [23], [27]. Notice that  $\tau$  increases exponentially with z due to electron tunneling from the

TABLE IMAIN PARAMETERS USED TO CALCULATE  $S_{VG}$  WITH (2). THE<br/>PARAMETERS USED TO COMPUTE  $\tau$  IN (2)ARE FROM [23] AND [27]

| Parameter                     | Value in Eq. 2                                    |

|-------------------------------|---------------------------------------------------|

| $C_{ox}$                      | $2 \cdot 10^{-2} \text{ F/m}^2$                   |

| $W{\cdot}L$                   | $0.5 \ \mu m^2$                                   |

| $E_C - E_F$                   | 1 meV                                             |

| $N_{BT}$ in SiO <sub>2</sub>  | $5 \cdot 10^{18} \text{ cm}^{-3} \text{ eV}^{-1}$ |

| $N_{BT}$ in HfO <sub>2</sub>  | $1 \cdot 10^{19} \text{ cm}^{-3} \text{ eV}^{-1}$ |

| $N_0$ (Band tail states)      | $1 \cdot 10^{20} \text{ cm}^{-3} \text{ eV}^{-1}$ |

| $\sigma_z$ (Band tail states) | 5 nm                                              |

| $\sigma_E$ (Band tail states) | 5 meV                                             |

channel into the dielectric. When the traps are in the channel, there is no electron tunneling barrier to reach the defects and therefore  $\tau$  is smaller compared to the case of dielectric traps. The K(z) term takes into account the electrostatic charge scaling between the trapped charge and the channel charge. It is equal to 1 when considering traps inside the channel (such as the band tail states), while it assumes a more complex form for dielectric traps in a gate-stack with an interlayer (see Table I in [25]). Considering an nMOS, we attempt to reproduce the effect of band tail states in the noise by inserting a trap distribution in the silicon channel with an exponential distribution in energy and space

$$N_{\rm BT} = N_0 \exp\left(\frac{z - z_0}{\sigma_z}\right) \exp\left(\frac{E_T - E_C}{\sigma_E}\right)$$

(3)

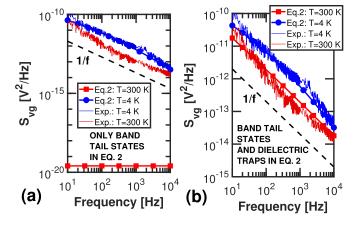

if  $z \leq z_0$  and  $E_T \leq E_C$ , and  $N_{\rm BT} = 0$  otherwise.  $N_0$  is the surface  $(z = z_0)$  concentration at the band edge,  $E_C$  is conduction band energy, and  $z_0$  and z are the positions of the Si/SiO<sub>2</sub> interface and of the band tail state, respectively, in the direction perpendicular to the channel. We first check the effect of band tail states on  $S_{vg}$  by using (3) into  $N_{BT}$  without inserting any dielectric trap. In this way, we highlight the contribution of band tail states to  $S_{vg}$ . This is shown in Fig. 12(a), where  $S_{vg}$  calculated with (2) at 300 and 4 K with only band tail states into  $N_{\rm BT}$  is compared to the measurements of Fig. 3(a). These states induce very low noise at 300 K because their occupation kinetics are fast and we only observe the flat part of a Lorentzian spectrum in the 10 Hz-10 kHz frequency range. On the other hand, the fluctuations of band tail states show up as 1/f noise at cryogenic temperatures with an amplitude compatible with the measurements. Let us now insert also dielectric traps in addition to the band tail states into  $N_{\rm BT}$ . Fig. 12(b) shows that the noise predicted by (2) at cryogenic temperature is only due to band tail states [same noise spectrum of Fig. 12(a)]. On the other hand, inserting dielectric traps into (2) reproduces the noise measurements of Fig. 3(a)at 300 K because the effect of dielectric traps dominates above cryogenic temperatures. This qualitative modeling approach supports the idea that band tail states can behave as traps at cryogenic temperatures, although more detailed analyses are necessary to reproduce all the features of low-temperature 1/f noise.

Fig. 12. Comparison between  $S_{vg}$  evaluated through (2) and the experimental results of Fig. 3(a) at T = 300 K and T = 4 K. In (a), we only have band tail states into  $N_{BT}$  of (2), while in (b), we also have dielectric traps in addition to the band tail states. The parameters used in (2) are listed in Table I.

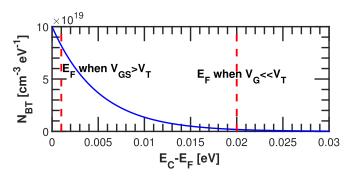

Fig. 13. Plot of the band tail states distribution in the energy. The Fermi level in inversion and far below the threshold are highlighted by dashed red lines. Notice that the amount of band tail states that fluctuate when  $V_G \ll V_T$  is much smaller compared to  $V_G > V_T$ .

# E. RTN Measurements in Subthreshold

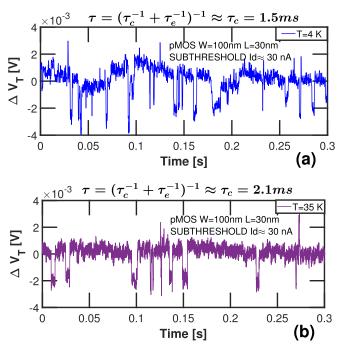

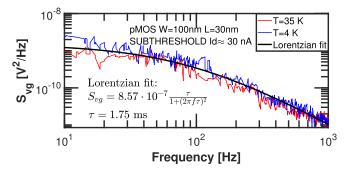

According to the explanation above, devices operating well below  $V_T$  should not have excess noise at cryogenic temperature since the Fermi level of the channel would not probe the band tail states (Fig. 13). Unfortunately, measuring the noise in subthreshold on the large-area devices yields a noise amplitude comparable to the instrumentation noise due to the reduction of  $S_{vg}$  with the device area [see (1)]. Therefore, to test this explanation, we identified a small-area device (W = 100 nm and L = 30 nm) where the random telegraph noise (RTN) waveform of the same defect is traced from 4 to 35 K without any increase in  $\Delta V_T = \Delta I_D / g_m$ (Fig. 14), where  $\Delta I_D$  is the fluctuation of the drain current from the DC value. The measurements refer to a foundry 28nm pMOS at  $I_D \approx 30$  nA ( $\approx 200$  mV below the threshold at 4 K). A similar RTN behavior is reported in [27] where it is shown that the capture/emission times of traps become independent of T at cryogenic temperatures (in line with Fig. 14). According to Fig. 4(a), one would expect a different S<sub>vg</sub> going from 35 to 4 K also in a small-area device. However, the 4 and 35 K  $S_{vg}$  measured at the same bias conditions of the RTN traces overlap with each other (Fig. 15), consistent with the hypothesis that we do not probe band tail states when we are well below  $V_T$ . Notice that  $S_{vg}$  of these small-area devices

Fig. 14. Time trace of  $\Delta V_T = \Delta i_d/g_m$  for the small-area (W = 100 nm and L = 30 nm) 28-nm technology pMOS at (a) T = 4 K and (b) T = 35 K. The trapping dynamics (i.e., capture/emission times) and the  $\Delta V_T$  amplitudes are very similar.

Fig. 15. Plot of  $S_{\rm vg}$  versus frequency for a small-area (W = 100 nm and L = 30 nm) 28-nm technology pMOS at T = 4 K and T = 35 K. Notice that the two curves overlap and are fitted with a Lorentzian PSD with  $\tau = 1.75$  ms (average between the  $\tau$  extracted from the traces in Fig. 14).

do not scale as T, because only a few traps contribute to the noise, and the integral  $\int_{-\infty}^{+\infty} f_T(1-f_T)dE_T$  is replaced by a sum over discrete states not leading to kT.

## **IV. CONCLUSION**

Noise measurements in a commercial 28-nm technology in the 370–4 K range show a significant excess 1/f noise at cryogenic temperatures, which cannot be explained by conventional noise models. This excess noise is present in both CNF and MF regimes. Our experiments exclude selfheating, electron heating, and the interaction with additional bulk dielectric defects as possible causes. Moreover, measurements of the same behavior on Ge-channel MOSFETs prove that this effect is not restricted to Si. This phenomenon strongly correlates with the SS saturation and the presence of band tail states that could act as traps at low temperatures. RTN and spectral noise measurements on small-area devices further confirm that this excess noise is not present when the channel Fermi level is not probing the band tail states. Our experiments thus provide a fundamental understanding of the abnormal 1/f noise increase observed in MOSFETs at cryogenic temperatures and highlight that band tail states could well be at the origin of the observed excess 1/f noise.

#### REFERENCES

- T. D. Ladd, F. Jelezko, R. Laflamme, Y. Nakamura, C. Monroe, and J. L. O'Brien, "Quantum computers," *Nature*, vol. 464, no. 7285, pp. 45–53, Mar. 2010, doi: 10.1038/nature08812.

- [2] D. J. Bernstein and T. Lange, "Post-quantum cryptography," *Nature*, vol. 549, no. 7671, pp. 188–194, Sep. 2017, doi: 10.1038/nature23461.

- [3] V. Moret-Bonillo, "Can artificial intelligence benefit from quantum computing?" *Prog. Artif. Intell.*, vol. 3, no. 2, pp. 89–105, Mar. 2015, doi: 10.1007/s13748-014-0059-0.

- [4] K. L. Brown, W. J. Munro, and V. M. Kendon, "Using quantum computers for quantum simulation," *Entropy*, vol. 12, no. 11, pp. 2268–2307, Nov. 2010, doi: 10.3390/e12112268.

- [5] D. P. Franke, J. S. Clarke, L. M. K. Vandersypen, and M. Veldhorst, "Rent's rule and extensibility in quantum computing," *Microprocessors Microsyst.*, vol. 67, pp. 1–7, Jun. 2019, doi: 10.1016/j.micpro.2019.02.006.

- [6] E. Charbon et al., "Cryo-CMOS for quantum computing," in *IEDM Tech. Dig.*, Dec. 2016, pp. 13.5.1–13.5.4, doi: 10.1109/IEDM.2016.7838410.

- [7] D. J. Reilly, "Engineering the quantum-classical interface of solid-state qubits," *NPJ Quantum Inf.*, vol. 1, no. 1, Oct. 2015, Art. no. 15011, doi: 10.1038/npjqi.2015.11.

- [8] B. Prabowo et al., "A 6-to-8 GHz 0.17 mW/qubit cryo-CMOS receiver for multiple spin qubit readout in 40 nm CMOS technology," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, vol. 64, Feb. 2021, pp. 212–214, doi: 10.1109/ISSCC42613.2021.9365848.

- [9] E. Paladino, Y. M. Galperin, G. Falci, and B. L. Altshuler, "1/f noise: Implications for solid-state quantum information," *Rev. Modern Phys.*, vol. 86, no. 2, pp. 361–418, Apr. 2014, doi: 10.1103/RevModPhys. 86.361.

- [10] J. Yoneda et al., "A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%," *Nature Nanotechnol.*, vol. 13, no. 2, pp. 102–106, Feb. 2018, doi: 10.1038/s41565-017-0014-x.

- [11] G. Ghibaudo, O. Roux, C. Nguyen-Duc, F. Balestra, and J. Brini, "Improved analysis of low frequency noise in field-effect MOS transistors," *Phys. Status Solidi A*, vol. 124, no. 2, pp. 571–581, Apr. 1991, doi: 10.1002/pssa.2211240225.

- [12] H. Oka et al., "Toward long-coherence-time Si spin qubit: The origin of low-frequency noise in cryo-CMOS," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1–2, doi: 10.1109/ VLSITechnology18217.2020.9265013.

- [13] B. C. Paz et al., "Performance and low-frequency noise of 22-nm FDSOI down to 4.2 K for cryogenic applications," *IEEE Trans. Electron Devices*, vol. 67, no. 11, pp. 4563–4567, Nov. 2020, doi: 10.1109/TED.2020.3021999.

- [14] H. Arimura et al., "Ge nFET with high electron mobility and superior PBTI reliability enabled by monolayer-Si surface passivation and La-induced interface dipole formation," in *IEDM Tech. Dig.*, Dec. 2015, pp. 21.6.1–21.6.4, doi: 10.1109/IEDM.2015.7409752.

- [15] A. Ortiz-Conde, F. J. G. Sánchez, J. J. Liou, A. Cerdeira, M. Estrada, and Y. Yue, "A review of recent MOSFET threshold voltage extraction methods," *Microelectron. Rel.*, vol. 42, nos. 4–5, pp. 583–596, Apr./May 2002, doi: 10.1016/S0026-2714(02)00027-6.

- [16] R. Asanovski et al., "New insights on the excess 1/f noise at cryogenic temperatures in 28 nm CMOS and Ge MOSFETs for quantum computing applications," in *IEDM Tech. Dig.*, 2022, pp. 711–714.

- [17] A. Beckers, F. Jazaeri, and C. Enz, "Theoretical limit of low temperature subthreshold swing in field-effect transistors," *IEEE Electron Device Lett.*, vol. 41, no. 2, pp. 276–279, Feb. 2020, doi: 10.1109/LED.2019.2963379.

- [18] P. A. T. Hart, M. Babaie, A. Vladimirescu, and F. Sebastiano, "Characterization and modeling of self-heating in nanometer bulk-CMOS at cryogenic temperatures," *IEEE J. Electron Devices Soc.*, vol. 9, pp. 891–901, 2021, doi: 10.1109/JEDS.2021.3116975.

- [19] R. Asanovski, P. Palestri, and L. Selmi, "On the accuracy of the formula used to extract trap density in MOSFETs from 1/f noise," *Solid-State Electron.*, vol. 194, Aug. 2022, Art. no. 108311, doi: 10.1016/j.sse.2022.108311.

- [20] M. Houssa et al., "Trap-assisted tunneling in high permittivity gate dielectric stacks," *Appl. Phys. Lett.*, vol. 87, no. 12, pp. 8615–8620, Jun. 2000, doi: 10.1063/1.373587.

- [21] M. Waltl, W. Goes, K. Rott, H. Reisinger, and T. Grasser, "A single-trap study of PBTI in SiON nMOS transistors: Similarities and differences to the NBTI/pMOS case," in *Proc. IEEE Int. Rel. Phys. Symp.*, Jun. 2014, pp. XT.18.1–XT.18.5, doi: 10.1109/IRPS.2014.6861195.

- [22] G. Rzepa et al., "Complete extraction of defect bands responsible for instabilities in n and pFinFETs," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2016, pp. 1–2, doi: 10.1109/VLSIT.2016.7573437.

- [23] G. Rzepa et al., "Comphy—A compact-physics framework for unified modeling of BTI," *Microelectron. Rel.*, vol. 85, pp. 49–65, Jun. 2018, doi: 10.1016/j.microrel.2018.04.002.

- [24] N. F. Mott and E. A. Davis, *Electronic Processes in Non-Crystalline Materials*. London, U.K.: Oxford Univ. Press, 2012.

- [25] R. Asanovski, P. Palestri, E. Caruso, and L. Selmi, "A comprehensive gate and drain trapping/detrapping noise model and its implications for thin-dielectric MOSFETs," *IEEE Trans. Electron Devices*, vol. 68, no. 10, pp. 4826–4833, Oct. 2021, doi: 10.1109/TED.2021.3104790.

- [26] R. Asanovski, P. Palestri, and L. Selmi, "Importance of charge trapping/detrapping involving the gate electrode on the noise currents of scaled MOSFETs," *IEEE Trans. Electron Devices*, vol. 69, no. 3, pp. 1313–1320, Mar. 2022, doi: 10.1109/TED.2022.3147158.

- [27] J. Michl et al., "Evidence of tunneling driven random telegraph noise in cryo-CMOS," in *IEDM Tech. Dig.*, Dec. 2021, pp. 31.3.1–31.3.4, doi: 10.1109/IEDM19574.2021.9720501.

Open Access funding provided by 'Università degli Studi di Modena e Reggio Emilia' within the CRUI CARE Agreement