IEEE TRANSACTIONS ON ELECTRON DEVICES

# Correlating Interface and Border Traps With Distinctive Features of *C*–*V* Curves in Vertical Al<sub>2</sub>O<sub>3</sub>/GaN MOS Capacitors

Nicolò Zagni<sup>®</sup>, *Member, IEEE*, Manuel Fregolent, Giovanni Verzellesi<sup>®</sup>, *Senior Member, IEEE*, Alberto Marcuzzi<sup>®</sup>, Carlo De Santi<sup>®</sup>, *Member, IEEE*, Gaudenzio Meneghesso<sup>®</sup>, *Fellow, IEEE*, Enrico Zanoni<sup>®</sup>, *Life Fellow, IEEE*, Eldad Bahat Treidel<sup>®</sup>, Enrico Brusaterra<sup>®</sup>, Frank Brunner, Oliver Hilt<sup>®</sup>, Matteo Meneghini<sup>®</sup>, *Senior Member, IEEE*, and Paolo Pavan<sup>®</sup>, *Senior Member, IEEE*

Abstract—In this article, we present an analysis of the correlation between interface traps (ITs) and border traps (BTs) on distinctive features of C-V curves in vertical Al<sub>2</sub>O<sub>3</sub>/gallium-nitride (GaN) MOS capacitors. First, pulsed C-V curves were characterized during the application of quiescent gate bias stresses of different magnitudes and signs. This characterization revealed four main distinctive features: 1) rightward rigid shift; 2) leftward rigid shift; 3) decrease of the  $\triangle C - \triangle V$  slope; and 4) formation of a hump in a gate bias range before the accumulation of electrons at the oxide/semiconductor interface. By means of a combined experimental/simulation analysis, these features were univocally attributed to specific ITs or BTs in the overall trap distribution. The simulation-aided analysis enhances the physical understanding of the C-V curves features and increases the dependability of the adopted IT measurement technique, allowing for a more rapid process optimization and device technology development.

Index Terms—  $Al_2O_3$ , border traps (BTs), interface traps (ITs), negative bias temperature instability (NBTI), positive bias temperature instability (PBTI), vertical gallium-nitride (GaN) metal-oxide-semiconductor capacitor (MOSCAP).

Manuscript received 2 October 2023; revised 7 November 2023; accepted 11 November 2023. This work was supported by the Electronic Component Systems for European Leadership Joint Undertaking (ECSEL JU) within the project "YESvGaN" under Grant 101007229. This Joint Undertaking was supported by the European Union's Horizon 2020 Research and Innovation Programme, and Germany, France, Belgium, Austria, Sweden, Spain, and Italy. The review of this article was arranged by Editor D. N. Nath. (*Nicolò Zagni and Manuel Fregolent contributed equally to this work.*) (*Corresponding authors: Nicolò Zagni; Manuel Fregolent.*)

Nicolò Zagni and Paolo Pavan are with the Department of Engineering "Enzo Ferrari," University of Modena and Reggio Emilia, 41125 Modena, Italy (e-mail: nicolo.zagni@unimore.it).

Manuel Fregolent, Alberto Marcuzzi, Carlo De Santi, Gaudenzio Meneghesso, Enrico Zanoni, and Matteo Meneghini are with the Department of Information Engineering, University of Padova, 35131 Padova, Italy (e-mail: manuel.fregolenti@dei.unipd.it).

Giovanni Verzellesi is with the Department of Sciences and Methods for Engineering (DISMI) and the EN&TECH Center, University of Modena and Reggio Emilia, 42122 Reggio Emilia, Italy.

Eldad Bahat Treidel, Enrico Brusaterra, Frank Brunner, and Oliver Hilt are with the Ferdinand-Braun-Institut (FBH), 12489 Berlin, Germany.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2023.3335032.

Digital Object Identifier 10.1109/TED.2023.3335032

#### I. INTRODUCTION

G ALLIUM-NITRIDE (GaN) field-effect transistors are currently being developed as switches for efficient power electronic converters. While several lateral GaN HEMT technologies have become commercially available, the achievement of reliable vertical devices is one of the goals that are more intensively pursued at the research level, for their advantages over lateral counterparts in high-power applications [1], [2].

In vertical transistors, the drift region develops through the device depth, so that increasing the maximum blocking voltage does not require the device to be extended laterally and the peak electric field in the OFF-state is far from the device surface. As a result, relatively small-area devices can be designed, which can operate in the kV range and are naturally immune from surface- and buffer-related, currentcollapse and dynamic  $R_{\rm ON}$  effects, that instead affect lateral device operation [3], [4], [5], [6], [7]. In addition, avalanche capability has been demonstrated in vertical GaN devices [8], [9], [10], [11] allowing for reliable, unclamped inductive switching in converter circuits [10].

As for the possible vertical transistor typologies, Fin MOSFETs [2], [12], vertical planar [13], and Trench MOSFETs [14], [15] are among the most targeted ones, providing feasible solutions for normally-OFF, low gate leakage, and high-voltage operation. Because these device technologies under development still suffer from significant trapping effects related to the MOS stack [16], [17], [18], control of the gate-stack quality is a critical issue that requires careful characterization during the process optimization loop. This calls for appropriate test structures and dependable experimental techniques for the characterization of the interface trap (IT) and border trap (BT) states, the latter being defects located in the oxide at 1–2 nm from the interface that can be easily reached by channel electrons through tunneling [16], [19], [20], [21], [22].

In this work, we present an analysis of the charge-trapping processes in quasi-vertical  $Al_2O_3/GaN$  MOS capacitors, extending some of the results presented in [23]. The experimental characterization relies on pulsed C-V measurements applied to devices in the fresh state as well as subjected

© 2023 The Authors. This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

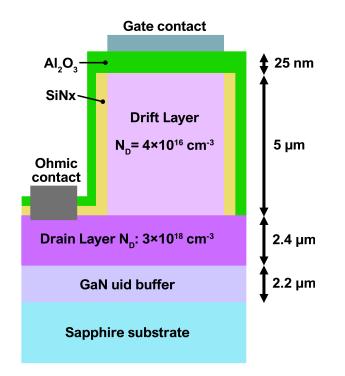

Fig. 1. Schematic cross section of the vertical  $Al_2O_3/GaN$  MOSCAP under test. The main dimensions are indicated.

to gate-bias stresses of both signs. The IT density  $(D_{\rm IT})$  is extracted in a wide energy range (>2 eV from the conductionband edge) of the GaN bandgap. The  $D_{\rm IT}$  extraction is performed by means of a modified method based on the photo-assisted C-V technique [24], [25], exploiting a large, negative gate voltage to discharge surface and BTs in place of UV illumination. Furthermore, the impact of ITs and BTs on the C-V curves and the accuracy of the extracted  $D_{\rm IT}$ distribution are assessed by means of device simulations. Simulations allow correlating different features of the C-Vcurves and the effects induced by gate bias stresses with the type (interface or border, donor or acceptor) as well as the energy range of responsible trap states.

The rest of this article is organized as follows. Section II describes the devices under test and the experimental characterization methodology. Section III includes the simulation setup, results, as well as a discussion to compare the experimental and simulation outcomes. Section IV draws the conclusions.

### **II. EXPERIMENTAL CHARACTERIZATION**

Characterized devices are quasi-vertical Al<sub>2</sub>O<sub>3</sub>/GaN MOS capacitors fabricated as test structures for a vertical GaN-based MOSFET technology [15]. The semiconductor armature of the MOS capacitor corresponds to the n<sup>-</sup> drift layer of the Trench MOSFET, with a doping density of  $4 \times 10^{16}$  cm<sup>-3</sup>. The GaN surface was pretreated with NH<sub>3</sub> plasma before the atomic layer deposition (ALD) of 25-nm Al<sub>2</sub>O<sub>3</sub> [26]. A schematic cross section is shown in Fig. 1, while more details on the fabrication process can be found in [11].

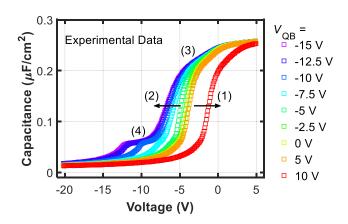

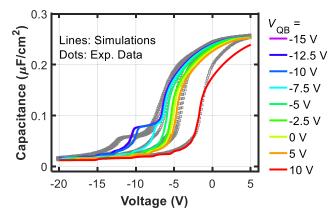

The MOS capacitor stability was characterized by monitoring the effects on the C-V curve of gate-quiescent-bias stresses ( $V_{QB}$ ) of both signs and different magnitudes. Fig. 2 collects the results from these experiments. Acquisition of the C-V curves exploited a variant of the experimental setup

Fig. 2. Pulsed *C*–*V* curves extracted at different gate quiescent stress biases ( $V_{\text{QB}}$ , see legend). (1)–(4) indicate the distinctive features of the *C*–*V* curves that are under investigation in this work: rightward rigid shift, leftward rigid shift, decrease of  $\Delta C/\Delta V$  slope, and hump formation.

described in detail in [15], [16], and [17] and summarized as follows. Each stress voltage  $V_{QB}$  is applied to the gate terminal for 100 s (to ensure reaching steady-state conditions), and then, periodically, every 1 s, the voltage is switched from  $V_{QB}$  to  $V_{M}$  for 1 ms.

The capacitance value is acquired by an analog *LCR* meter at 1 MHz and 0.1-V ac frequency and amplitude. To improve the signal-to-noise ratio, for each pulse at  $V_{\rm M}$ , capacitance is obtained by averaging the readings for  $\approx 0.5$  ms after settlement of the instrument.  $V_{\rm M}$  is swept between -20 and 5 V to characterize a full C-V curve. The sequence is repeated for each  $V_{\text{QB}}$ , ranging from -15 to +10 V. Total stress time is thus about 350 s for each  $V_{QB}$  value. Four distinctive features, (1)–(4), of the C-V curves of the MOS capacitor can be identified in Fig. 2. Specifically: i) for small stress voltages  $(-2.5 \text{ V} < V_{\text{QB}} < 5 \text{ V})$ , regardless of the voltage sign, the C-V curves are stable and almost superimposed one to each other [26]; ii) for larger, positive bias (5 V  $< V_{OB} < 10$  V), the C-V curve is shifted rightward rigidly [feature (1)]; and iii) for larger, negative bias  $(-15 < V_{OB} < -2.5 \text{ V})$ , the C-Vcurve is shifted leftward [feature (2)] with related decrease in the  $\Delta C/\Delta V$  slope [feature (3)] and formation of a hump [feature (4)] in the low-voltage end of the curve. It should be stressed that from a practical point of view, stress condition i) corresponds to the typical bias range of the gate terminal of a normally-OFF transistor (i.e., with positive threshold voltage,  $V_{\rm T}$ ). In addition, feature (1), i.e., the C-V rightward rigid shift, represents a critical limit to the  $V_{\rm T}$  stability in MOSFETs.

To characterize the Al<sub>2</sub>O<sub>3</sub>/GaN interface and extract the density of ITs ( $D_{\text{IT}}$ ), a modified version of the photo-assisted C-V method was adopted [23]. The method is based on a careful comparison of the C-V measurements in detrapped and trapped conditions [24], [25]. Different from [24] and [25], however, a long, negative gate bias is used in place of UV illumination to induce the discharging of traps. This modified methodology allows to characterize the C-V curves under different trap filling conditions with a much simpler setup compared to the one required for UV illumination. However, in the latter case, electrons trapped in BTs are emitted thanks to the energy provided by the illumination itself, whereas in the former one, the electrical stress discharges the BTs by electron tunneling into the semiconductor. Regarding ITs, both the

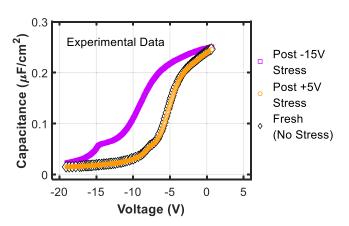

Fig. 3. Fast C-V curves acquired after 1000-s stress at -15 (purple squares) and 5 V (orange circles) used to extract the  $D_{\text{IT}}$  distribution shown in Fig. 4 with the modified photo-assisted C-V method described in the text. Fresh C-V, i.e., acquired before the stress curve (black diamonds) is also shown for reference.

UV illumination as well as the long negative electrical stress cause detrapping by electron emission to the semiconductor conduction band. This point is further discussed later on.

A strong negative bias of -15 V was applied to the MOS capacitor for 1000 s, and a fast C-V curve was acquired (i.e., with a 10-ms sweep) by using the experimental setup described in [18] and [19]. It is important to observe that while this stress condition was applied with the specific intent of emptying the traps (i.e., donor-like traps become positively charged and acceptor-like become neutral), the C-V acquired after stress is still subjected to trap-related features. As a matter of fact, during the voltage sweep of the measurement itself, ITs change their charge state (i.e., donor-like traps become neutral and acceptor-like traps become negatively charged) due to the capture of electrons at the semiconductor surface. Conversely, the BT state is not altered by the fast C-V measurement.

Additionally, by applying +5 V to the gate for 1000 s, another fast C-V curve is recorded with the same setup as for the negative stress. The two C-V curves are shown in Fig. 3. Fresh C-V curve, i.e., acquired before stress, is also shown for reference. As can be noted from Fig. 3, the post +5-V stress C-V curve almost overlaps with the fresh one, indicating the excellent robustness of the ALD-deposited Al<sub>2</sub>O<sub>3</sub> layer against forward bias stress.

$D_{\rm IT}$  is obtained from the slope of the  $\Delta V$  versus  $\psi_{\rm s}$  curve, where  $\Delta V$  is the voltage difference obtained at each capacitance value between the "Post -15-V" and "Post +5-V" curves in Fig. 3, and  $\psi_{\rm s}$  is the surface potential obtained as in [23]. That is,

$$D_{\rm IT} = \frac{C_{\rm ox}}{qA} \left( \frac{\mathrm{d}\Delta V}{\mathrm{d}\psi_{\rm s}} \right) \tag{1a}$$

$$\psi_{\rm s} = \frac{q\varepsilon_{\rm s} N_{\rm D} A^2}{2C_{\rm s}(V)^2} \tag{1b}$$

where  $C_{ox}$  is the oxide capacitance, A is the area of the metal-oxide-semiconductor capacitor (MOSCAP), q is the elementary charge,  $\varepsilon_s$  is the dielectric constant of the semiconductor,  $N_D$  is the doping of the drift layer, and  $C_s$  is the semiconductor capacitance (obtained from the measured gate capacitance  $C_{\text{meas}}$  as  $C_s^{-1} = C_{\text{meas}}^{-1} - C_{\text{ox}}^{-1}$ ).

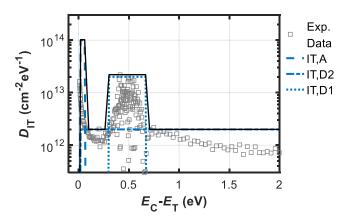

Fig. 4.  $D_{\text{IT}}$  versus  $E_{\text{C}}-E_{\text{T}}$  used in the simulations to reproduce the experimental pulsed C-V curves (see Fig. 6). Black solid line is the IT distribution, and blue dashed, dashed-dotted, and dotted lines are the three single boxes contributing to the overall distribution. Experimental data are reported as gray symbols for comparison.

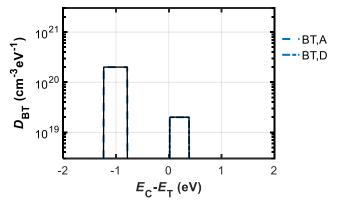

Fig. 5.  $D_{\text{BT}}$  versus  $E_{\text{C}}-E_{\text{T}}$  used in the simulations to reproduce the experimental pulsed C-V curves (see Fig. 6). Black solid line is the BT distribution, and blue dashed and dashed-dotted lines are the single boxes contributing to the overall distribution (see legend).

The trap distribution versus trap energy (with respect to the conduction band edge,  $E_{\rm C}$ ) is reported in Fig. 4 for a typical device (gray symbols). As it can be seen, the obtained  $D_{\rm IT}$  covers a remarkedly wide range of >2 eV from  $E_{\rm C}$ , and it shows the presence of a 2 × 10<sup>13</sup> cm<sup>-2</sup>·eV<sup>-1</sup> peak at about 0.5 V below  $E_{\rm C}$ . This peak overlaps with the typical U-shaped continuum of interface states rapidly increasing at the band edges (here, only the portion near  $E_{\rm C}$  can be probed by this method). Deep ITs (i.e., with energies between 1 and 2 eV) extracted in Fig. 4 effectively emit electrons (and can thus be probed by this method). We attribute this to an electric-field-enhancement mechanism reducing emission times (e.g., Poole–Frenkel). The electrical behavior of traps (i.e., acceptor- or donor-like) can only be clarified by calibrated simulations, as discussed in Section III.

#### **III. DEVICE SIMULATIONS AND DISCUSSION**

The 2-D numerical device simulations were performed with the SDevice simulator included in the Synopsys TCAD suite [27] aimed at: 1) analyze the impact of ITs and BTs on the features (1)–(4) induced by positive and negative stresses on the C-V curves discussed in Section II and 2) provide a cross-validity check of the method for  $D_{\text{IT}}$  extraction proposed in [23]. Simulations account for ITs using a fully dynamic Shockley-Read-Hall (SRH) model (no quasi-static approximation), self-consistently coupled to the drift–diffusion

Fig. 6. Simulated C-V curves (colored solid lines) obtained with the same method as the experimental data (gray symbols) with different gate quiescent stress biases ( $V_{\text{QB}}$ , see legend). Features of the C-V curves observed in the measurements are correctly reproduced by the simulations.

TABLE I IT AND BTS PARAMETERS USED IN THE SIMULATIONS

| Label | Areal<br>Density ( <i>D</i> ,<br>cm <sup>-2</sup> .eV <sup>-1</sup> ) | Volume<br>Density (D,<br>cm <sup>-3</sup> .eV <sup>-1</sup> ) | Energy<br>Mean (eV)† | Energy<br>Spread (eV) |

|-------|-----------------------------------------------------------------------|---------------------------------------------------------------|----------------------|-----------------------|

| IT,A  | $10^{14}$                                                             | //                                                            | 0                    | 0.2                   |

| IT,D2 | $2 \times 10^{12}$                                                    | //                                                            | 1.7                  | 3.4                   |

| IT,D1 | $2 \times 10^{13}$                                                    | //                                                            | 0.5                  | 0.4                   |

| BT,A  | //                                                                    | $2 \times 10^{20}$                                            | -1                   | 0.5                   |

| BT,D  | //                                                                    | $2 \times 10^{19}$                                            | 0.2                  | 0.4                   |

$\dagger$ Positive (negative) energy means below (above)  $E_{\rm C}$ .

model. On the other hand, BTs are placed into the Al<sub>2</sub>O<sub>3</sub> region and are linked to the semiconductor surface through a Wentzel–Kramer–Brillouin (WKB)-approximation-based non-local tunneling model ("tunneling into traps" model in [27]).

The energy distributions of ITs and BTs that were implemented in the simulator are shown in Figs. 4 and 5, respectively. Black solid lines are used for the overall IT and BT distributions yielding the best agreement with experimental data (see Fig. 6), and blue lines with different styles (see legend) are used instead for indicating the various components of the adopted distributions that, as later discussed, can be linked one-to-one with the distinctive features of the C-V curves. Box-like distributions were adopted for easier parameterization. Trap parameters are summarized in Table I.

Fig. 6 shows the C-V curves obtained by simulations incorporating the IT and BT distributions depicted with the black solid line in Figs. 4 and 5. In the simulator, the gate voltage is swept with the same pulse sequence used in the experiments, while the capacitance is obtained through a linearized, small-signal ac analysis. As can be noted from Fig. 6, a good agreement with experimental C-V curves is achieved, specifically, all the (1)-(4) features induced by positive and negative gate bias stresses are successfully captured by simulations. This was achieved by: 1) using an IT distribution that reproduces, within a box-wise approximation, the measured  $D_{\rm IT}$  (compare the black and gray solid lines in Fig. 4) and 2) including two BT boxes with density and energy position that have been used as fitting parameters. As will be clarified by the subsequent sensitivity analysis, BTs induce only rigid shifts in the C-V curves (of positive and negative signs for positive and negative gate bias stresses,

respectively). However, because the "photo-assisted C-V"-like method described in Section II allows only to determine the differential variations of the post -15-V and post +5-V stress C-V curves in Fig. 3, BT distributions cannot be directly characterized. Thus, the relative parameters are obtained by fitting the simulations with experimental data. On the other hand, simulations confirm that the  $\Delta C/\Delta V$  slope as well as the hump centered at about 0.5 eV below  $E_{\rm C}$  is governed solely by ITs.

For these reasons, results in Fig. 6 provide a meaningful, accuracy-validation procedure for the adopted  $D_{\text{IT}}$  measurement method, indicating also that the energy depth of the IT distribution probed by this technique is sufficient to explain trapping effects occurring in a wide range of gate biases.

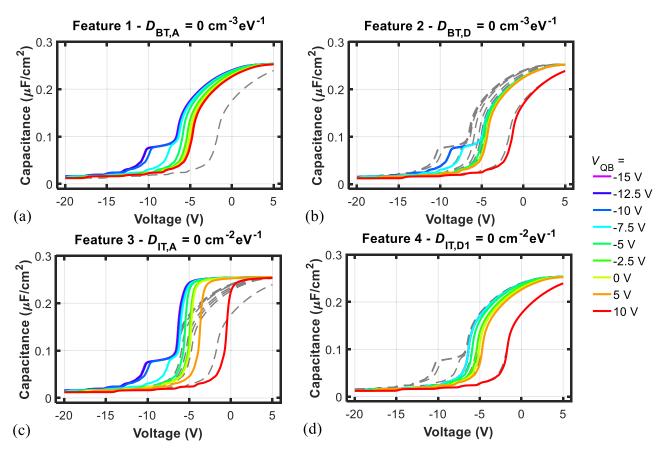

With respect to the optimal distributions yielding the results of Fig. 6, simulations with varied IT and BT boxes have been carried out. More specifically, we performed a new set of simulations by selectively setting the concentration of each of the trap boxes in the distribution to 0. By this way, we obtain a one-to-one link between the distinctive features (1)–(4) induced by gate bias stresses on the C-V curves and the single components of the overall trap distribution. For simplicity, we did not include any field-enhancement emission model in the simulation setup. For this reason, IT,D2 traps with energies  $>\approx 1$  eV remain always neutral in the simulations.

Results of the sensitivity analysis are reported in Fig. 7. As discussed previously, Fig. 7(a)-(d) allows to immediately identify the correspondence between the observed (1)–(4) features of C-V curves and different components of the overall IT and BT distributions. In fact, Fig. 7 allows observing that removing a specific BT or IT box in the distribution consequently makes the simulations fail to capture one (and only one) distinctive feature in the C-V curves. On the other hand, results in Fig. 7 allow to conclude that feature: (1) that is, the rightward rigid shift, is due to the BTs acting as acceptors, BT,A. This information is critically important for ALD layer optimization achieved through BT reduction; (2) that is, the leftward rigid shift, is due to the BTs acting as donors, BT,D; (3) that is, the decrease of  $\Delta C/\Delta V$  slope, is due to the ITs acting as acceptors, IT,A. This is important as subthreshold slope degradation leads to increased switching losses; and (4) that is, the formation of a hump in the gate bias range before the accumulation of channel electrons, is due to the ITs acting as donors, IT,D1.

From a practical point of view, features (1) and (3) are the most relevant ones, as the former leads to positive  $V_{\rm T}$ shift and the latter to switching losses. Therefore, for practical application of the investigated test structures in the epitaxy of GaN vertical transistors, it is of utmost importance to reduce acceptor traps—either at the interface or in the gate oxide—to minimize  $V_{\rm T}$  shift and reduce switching losses.

The role of IT,D1 traps in determining feature (4) is explained as follows. When applying a large negative quiescent bias (e.g., -15 V), the Fermi levels drop below the trap energy levels, thus positively charging these traps as a consequence of electron emission according to the SRH model.

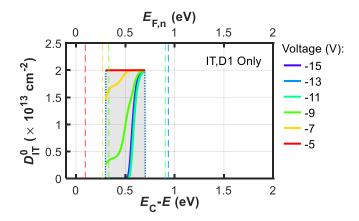

During the capacitance measurement, as the voltage is swept from -20 to +5 V, the position of the Fermi level varies according to the bias and the state of the positively charged donor-like ITs consequently changes. This is illustrated in Fig. 8, showing the neutralized donor density  $(D_{\rm IT}^0)$

Fig. 7. Simulated C-V curves with different IT and BT concentrations with respect to the calibration setup, the corresponding results of which are reported with dashed lines. The sensitivity analysis highlights the role of different components of the trap distribution on the features (1)–(4) of the C-V curves identified in the text: (a)  $D_{BT,A} = 0 \text{ cm}^{-3} \cdot \text{eV}^{-1}$  leads to no positive rigid shift; (b)  $D_{BT,D} = 0 \text{ cm}^{-3} \cdot \text{eV}^{-1}$  leads to sharp  $\Delta C/\Delta V$  slope; and (d)  $D_{IT,D1} = 0 \text{ cm}^{-2} \cdot \text{eV}^{-1}$  leads to no hump formation for negative  $V_{QB}$ .

Fig. 8. Ionized trapped charge  $(D_{\text{IT}}^0)$  due to IT,D1 only versus energy referred to GaN conduction band edge  $(E_{\text{C}})$  for different voltage bias (see legend) extracted from the simulation of the *C*-*V* curve with  $V_{\text{QB}} = -15$  V. The box-like distribution of IT,D1 defined in Table I is reported for reference (shaded region). The electron quasi-Fermi level ( $E_{\text{F,n}}$ ) for each bias is also shown (dashed lines).

versus energy referred to  $E_{\rm C}$  as in Fig. 4 for the bias range between -15 and -5 V extracted from the simulation of the *C*-*V* curve with  $V_{\rm QB} = -15$  V (see Fig. 6). To focus on the understanding of feature (4), the  $D_{\rm IT}^0$  extracted from the simulations is the one relative to IT,D1 only. The "box-like" IT,D1 distribution defined in Table I is also reported for reference. Fig. 8 also shows the position of the electron quasi-Fermi level  $(E_{F,n})$  extracted from the simulator for the same bias range. Clearly from Fig. 8, it is possible to observe how  $D_{IT}^0$  increases as the bias is increased, and therefore,  $E_{F,n}$  moves closer to  $E_C$ . This correlates with the reduced positive charge at the origin of the ledge. Specifically, these traps get neutralized as they progressively capture electrons coming from the bulk of the drift layer and accumulating at the Al<sub>2</sub>O<sub>3</sub>/GaN interface. The reducing positive charge progressively shifts the accumulation towards more positive bias (i.e., it is necessary to apply a more positive voltage to increase the accumulation capacitance), and this is appreciated in the C-V curves as feature (4).

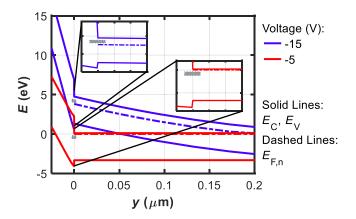

Feature (4) can also be understood from the band diagrams shown in Fig. 9 taken at different biases and extracted from the simulation of the C-V curves with  $V_{QB} = -15$  V. The shaded energy region in Fig. 9 is plotted in the energy range of IT,D1 distribution (see Figs. 4 and 8). From Fig. 9, one can observe that at V = -15 V, ITD,1 is above  $E_{F,n}$ , and thus, it is empty of electrons. Conversely, at V = -5 V, ITD,1 is below  $E_{F,n}$ , and thus, it is full of electrons. This correlates with the results shown in Fig. 8 and further explains the formation of the hump in Fig. 6 as due to the modulation of IT,D1 trap occupation.

The combined experimental/simulation analysis carried out in this work allows clearly pinpointing the single trap contributions responsible for each of the distinctive features of the pulsed C-V curves. While the simulated IT distribution

Fig. 9. Band diagrams along device depth (*y*) at different voltages (see legend) extracted from the simulation of the C-V curves with  $V_{\text{QB}} = -15$  V. The gray-shaded region is plotted in the energy range of the ITD,1 distribution (see Figs. 4 and 8). At V = -15 V (-5 V), ITD,1 is above (below)  $E_{\text{E,n}}$ , and thus, it is empty (full) of electrons (see insets).

reproduces the one extracted from the modified photo-assisted C-V measurements, providing a means to validate the adopted method, the setup also includes the BTs responsible for the observed rightward/leftward shifts of the C-V curves, which cannot be extracted with the previous method, thus also augmenting the information obtained from the experiments.

## IV. CONCLUSION

Vertical Al<sub>2</sub>O<sub>3</sub>/GaN MOSCAPs were characterized by means of pulsed C-V curves extracted while stressing at both negative and positive quiescent gate biases. The characterization revealed four main distinctive features of the C-Vcurves induced by different stress biases, namely, rightward and leftward rigid shifts, decrease of the  $\Delta C/\Delta V$  slope, and formation of a hump. By means of a combined experimental and simulation analysis, these features were attributed to either ITs or BTs (i.e., in the Al<sub>2</sub>O<sub>3</sub> within few nanometers from the interface). The enhanced physical understanding of the distinctive features of the C-V curves and the increased dependability of the adopted  $D_{\rm IT}$  measurement technique obtained with the simulations is instrumental for a more rapid process optimization and device technology development. In this sense, for proper operation of these test structures in GaN normally-OFF vertical transistors, it is primarily important to reduce acceptor traps-either at the interface or in the gate oxide—to minimize  $V_{\rm T}$  instability and reduce switching losses.

#### REFERENCES

- M. Meneghini et al., "GaN-based power devices: Physics, reliability, and perspectives," J. Appl. Phys., vol. 130, no. 18, Nov. 2021, Art. no. 181101, doi: 10.1063/5.0061354.

- [2] H. Fu, K. Fu, S. Chowdhury, T. Palacios, and Y. Zhao, "Vertical GaN power devices: Device principles and fabrication technologies—Part II," *IEEE Trans. Electron Devices*, vol. 68, no. 7, pp. 3212–3222, Jul. 2021, doi: 10.1109/TED.2021.3083209.

- [3] J. A. del Alamo and E. S. Lee, "Stability and reliability of lateral GaN power field-effect transistors," *IEEE Trans. Electron Devices*, vol. 66, no. 11, pp. 4578–4590, Nov. 2019, doi: 10.1109/TED.2019.2931718.

- [4] N. Modolo et al., "A physics-based approach to model hot-electron trapping kinetics in p-GaN HEMTs," *IEEE Electron Device Lett.*, vol. 42, no. 5, pp. 673–676, May 2021, doi: 10.1109/LED.2021.3067796.

- [5] A. Chini et al., "Gate-bias induced RON instability in p-GaN power HEMTs," *IEEE Electron Device Lett.*, vol. 44, no. 6, pp. 915–918, Jun. 2023, doi: 10.1109/LED.2023.3265503.

- [6] N. Zagni et al., "'Hole redistribution' model explaining the thermally activated R<sub>ON</sub> stress/recovery transients in carbon-doped AlGaN/GaN power MIS-HEMTs," *IEEE Trans. Electron Devices*, vol. 68, no. 2, pp. 697–703, Feb. 2021, doi: 10.1109/TED.2020.3045683.

- [7] M. Cioni, N. Zagni, F. Iucolano, M. Moschetti, G. Verzellesi, and A. Chini, "Partial recovery of dynamic RON versus OFF-state stress voltage in p-GaN gate AlGaN/GaN power HEMTs," *IEEE Trans. Electron Devices*, vol. 68, no. 10, pp. 4862–4868, Oct. 2021, doi: 10.1109/TED.2021.3105075.

- [8] K. Ohnishi et al., "Vertical GaN p<sup>+</sup>-n junction diode with ideal avalanche capability grown by halide vapor phase epitaxy," *Appl. Phys. Lett.*, vol. 119, no. 15, Oct. 2021, Art. no. 152102, doi: 10.1063/5.0066139.

- [9] Z. Bian, K. Zeng, and S. Chowdhury, "2.8 kV avalanche in vertical GaN PN diode utilizing field plate on hydrogen passivated P-layer," *IEEE Electron Device Lett.*, vol. 43, no. 4, pp. 596–599, Apr. 2022, doi: 10.1109/LED.2022.3149748.

- [10] J. Liu et al., "1.2 kV vertical GaN fin JFETs with robust avalanche and fast switching capabilities," in *IEDM Tech. Dig.*, Dec. 2020, p. 23, doi: 10.1109/IEDM13553.2020.9372048.

- [11] E. Brusaterra et al., "Optimization of vertical GaN drift region layers for avalanche and punch-through pn-diodes," *IEEE Electron Device Lett.*, vol. 44, no. 3, pp. 388–391, Mar. 2023, doi: 10.1109/LED.2023.3234101.

- [12] Y. Zhang et al., "Large-area 1.2-kV GaN vertical power FinFETs with a record switching figure of merit," *IEEE Electron Device Lett.*, vol. 40, no. 1, pp. 75–78, Jan. 2019, doi: 10.1109/LED.2018.2880306.

- [13] R. Tanaka, S. Takashima, K. Ueno, H. Matsuyama, and M. Edo, "Demonstration of 1200 V/1.4 mΩ cm<sup>2</sup> vertical GaN planar MOSFET fabricated by an all ion implantation process," *Jpn. J. Appl. Phys.*, vol. 59, Apr. 2020, Art. no. SGGD02.

- [14] T. Oka, "Recent development of vertical GaN power devices," Jpn. J. Appl. Phys., vol. 58, Apr. 2019, Art. no. SB0805.

- [15] E. B. Treidel et al., "On the conduction properties of vertical GaN n-channel trench MISFETs," *IEEE J. Electron Devices Soc.*, vol. 9, pp. 215–228, 2021, doi: 10.1109/JEDS.2021.3056697.

- [16] M. Ruzzarin et al., "Highly stable threshold voltage in GaN nanowire FETs: The advantages of p-GaN channel/Al<sub>2</sub>O<sub>3</sub> gate insulator," *Appl. Phys. Lett.*, vol. 117, no. 20, Nov. 2020, Art. no. 203501, doi: 10.1063/5.0027922.

- [17] K. Mukherjee et al., "Challenges and perspectives for vertical GaN-on-Si trench MOS reliability: From leakage current analysis to gate stack optimization," *Materials*, vol. 14, no. 9, p. 2316, Apr. 2021.

- [18] K. Mukherjee et al., "Analysis of threshold voltage instabilities in semivertical GaN-on-Si FETs," *Appl. Phys. Exp.*, vol. 13, no. 2, Feb. 2020, Art. no. 024004.

- [19] M. Fregolent et al., "Logarithmic trapping and detrapping in β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs: Experimental analysis and modeling," *Appl. Phys. Lett.*, vol. 120, no. 16, Apr. 2022, Art. no. 163502, doi: 10.1063/5. 0085068.

- [20] D. M. Fleetwood, "Border traps' in MOS devices," *IEEE Trans. Nucl. Sci.*, vol. 39, no. 2, pp. 269–271, Apr. 1992, doi: 10.1109/23. 277495.

- [21] F. Masin et al., "Non-monotonic threshold voltage variation in 4H-SiC metal-oxide-semiconductor field-effect transistor: Investigation and modeling," J. Appl. Phys., vol. 130, no. 14, Oct. 2021, Art. no. 145702, doi: 10.1063/5.0057285.

- [22] P. Pavan et al., "The impact of interface and border traps on currentvoltage, capacitance-voltage, and split-CV mobility measurements in InGaAs MOSFETs," *Phys. Status Solidi* (A), vol. 214, no. 3, Mar. 2017, Art. no. 1600592.

- [23] M. Fregolent et al., "Trapping in Al<sub>2</sub>O<sub>3</sub>/GaN MOScaps investigated by fast capacitive techniques," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Mar. 2023, pp. 1–5, doi: 10.1109/IRPS48203.2023.10117719.

- [24] B. L. Swenson and U. K. Mishra, "Photoassisted high-frequency capacitance-voltage characterization of the Si<sub>3</sub>N<sub>4</sub>/GaN interface," *J. Appl. Phys.*, vol. 106, no. 6, Sep. 2009, Art. no. 064902, doi: 10.1063/1.3224852.

- [25] K. Mukherjee et al., "Study and characterization of GaN MOS capacitors: Planar vs trench topographies," *Appl. Phys. Lett.*, vol. 120, no. 14, Apr. 2022, Art. no. 143501, doi: 10.1063/5.0087245.

- [26] L. Tadmor et al., "Effects of post metallization annealing on Al<sub>2</sub>O<sub>3</sub> atomic layer deposition on n-GaN," *Semiconductor Sci. Technol.*, vol. 38, no. 1, Dec. 2022, Art. no. 015006.

- [27] Sentaurus SDevice Manual, Synopsys, Mountain View, CA, USA, Jun. 2021.