#### Università degli Studi di Modena e Reggio Emilia Dipartimento di Ingegneria "Enzo Ferrari"

# INTERNATIONAL DOCTORATE IN INFORMATION AND COMMUNICATION TECHNOLOGIES XXXIV CYCLE

# Innovative Energy-Efficient Circuits Enabled by Resistive Memory devices for Secure In-Memory Computing

Candidate:

Tommaso ZANOTTI

Advisor:

Prof. Francesco Maria PUGLISI

Co-Advisor:

Prof. Paolo PAVAN

Director of the PhD school: Prof. Sonia BERGAMASCHI

## Acknowledgments

I would like to express my deepest gratitude to my primary supervisor, prof. Francesco Maria Puglisi, for his guidance and continuous support during the three years of the PhD program.

Also, I would like to thank prof. Paolo Pavan for his support, advice, and proficuous discussions together with fellow researcher and master thesis students of the Electronics group at UniMORE.

My special thanks also go to my love, Chiara Bachechi, for her encouragement to pursue the PhD, for always keeping me motivated and for her love and support through the years.

Finally, I wish to extend my special thanks to my parents and the rest of my family, as this achievement would have never been possible without their endless encouragement and support.

# Contents

| Acknowledgments |                       |                                                              |                                                     |    |  |

|-----------------|-----------------------|--------------------------------------------------------------|-----------------------------------------------------|----|--|

| $\mathbf{A}$    | bstra                 | $\mathbf{ct}$                                                |                                                     | ix |  |

| 1               | Res                   | sistive                                                      | memory devices for the future of computing and      |    |  |

|                 | security applications |                                                              |                                                     |    |  |

|                 | 1.1                   | Ultra-                                                       | low power computing and security functions          | 1  |  |

|                 |                       | 1.1.1                                                        | Beyond Moore's law                                  | 1  |  |

|                 |                       | 1.1.2                                                        | In-memory computing                                 | 2  |  |

|                 |                       | 1.1.3                                                        | Emerging nonvolatile memory technologies            | 5  |  |

|                 |                       | 1.1.4                                                        | Hardware security building blocks                   | 8  |  |

|                 |                       | 1.1.5                                                        | The focus of this thesis                            | 11 |  |

|                 | 1.2                   | Resist                                                       | ive Random Access Memories                          | 11 |  |

|                 |                       | 1.2.1                                                        | Metal Oxide MIM devices                             | 12 |  |

|                 |                       | 1.2.2                                                        | Stochastic behavior of RRAM devices                 | 15 |  |

|                 | 1.3                   | 1.3 In-memory computing with state-of-the-art RRAM devices . |                                                     |    |  |

|                 |                       | 1.3.1                                                        | Logic-in-Memory                                     | 18 |  |

|                 |                       | 1.3.2                                                        | Analog computing with memory arrays for deep neural |    |  |

|                 |                       |                                                              | networks                                            | 20 |  |

|                 | 1.4                   | True I                                                       | Random Number generator circuits                    | 23 |  |

|                                                          | 1.5               | Thesis                                           | structure                                           | 27  |  |  |

|----------------------------------------------------------|-------------------|--------------------------------------------------|-----------------------------------------------------|-----|--|--|

| <b>2</b>                                                 | RR                | AM pł                                            | nysics-based compact modeling                       | 29  |  |  |

|                                                          | 2.1               | RRAM                                             | I compact models features and requirements          | 29  |  |  |

|                                                          | 2.2               | 2 The UniMORE RRAM physics-based compact model . |                                                     |     |  |  |

|                                                          |                   | 2.2.1                                            | Compact model description                           | 33  |  |  |

|                                                          |                   | 2.2.2                                            | Implementation following the best practices         | 55  |  |  |

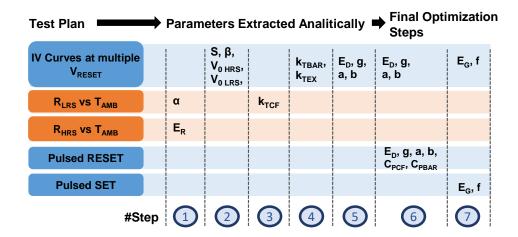

|                                                          | 2.3               | nated parameter extraction procedure             | 56                                                  |     |  |  |

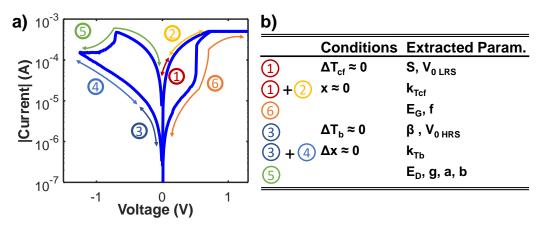

|                                                          |                   | 2.3.1                                            | Design of experiments                               | 57  |  |  |

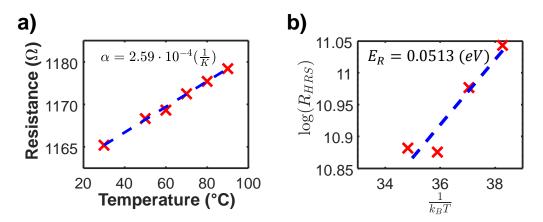

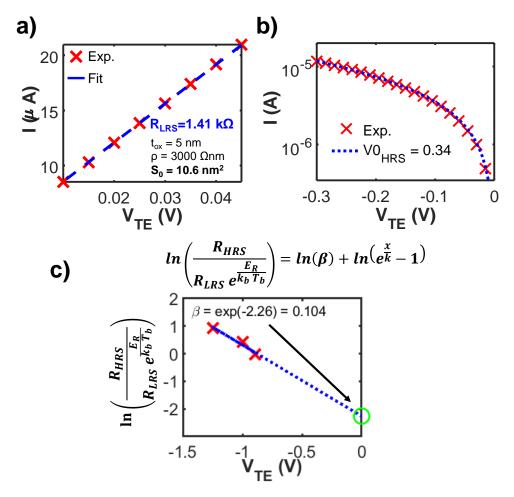

|                                                          |                   | 2.3.2                                            | Data processing                                     | 59  |  |  |

|                                                          |                   | 2.3.3                                            | Parameter optimization                              | 65  |  |  |

|                                                          |                   | 2.3.4                                            | Simplified parameter extraction procedure from data |     |  |  |

|                                                          |                   |                                                  | from the literature                                 | 68  |  |  |

|                                                          | 2.4               | Relate                                           | ed published works                                  | 75  |  |  |

| 3                                                        | Stu               | dy and                                           | development of RRAM-based in-memory comput-         |     |  |  |

|                                                          | ing architectures |                                                  |                                                     |     |  |  |

|                                                          | 3.1               | IMPLY                                            | Y LiM architectures                                 | 78  |  |  |

|                                                          |                   | 3.1.1                                            | Working principle                                   | 79  |  |  |

|                                                          |                   | 3.1.2                                            | Reliability analysis                                | 80  |  |  |

|                                                          | 3.2               | Smart                                            | IMPLY architecture                                  | 89  |  |  |

|                                                          |                   | 3.2.1                                            | Working principle                                   | 89  |  |  |

|                                                          |                   | 3.2.2                                            | Reliability analysis                                | 93  |  |  |

|                                                          |                   | 3.2.3                                            | Multi-input IMPLY operation                         | 94  |  |  |

|                                                          |                   | 3.2.4                                            | Performance Benchmarking                            | 99  |  |  |

|                                                          | 3.3               | Low-b                                            | it precision neural networks                        | 119 |  |  |

| 3.4 Merging multiple computing paradigms on the same men |                   |                                                  |                                                     |     |  |  |

|                                                          |                   | arrav                                            |                                                     | 128 |  |  |

|                  | 3.5          | Related published works                    | 134 |

|------------------|--------------|--------------------------------------------|-----|

| 4                | Stu          | dy of RTN-based TRNGs                      | 135 |

|                  | 4.1          | RTN-based TRNGs circuits                   | 136 |

|                  | 4.2          | Performance evaluation                     | 141 |

|                  |              | 4.2.1 Experimental data                    | 141 |

|                  |              | 4.2.2 Randomness tests results             | 146 |

|                  | 4.3          | Device-circuit co-optimization             | 150 |

|                  | 4.4          | Related published works                    | 153 |

| $\mathbf{C}_{0}$ | onclu        | sions                                      | 155 |

|                  | Disc         | ussion                                     | 155 |

|                  | Futu         | re Outlook                                 | 159 |

| a                | Uni          | MORE RRAM physics-based compact model v2.0 | 161 |

|                  | I            | Compact Model                              | 161 |

|                  | II           | Disciplines [112]                          | 193 |

| Bi               | bliog        | graphy                                     | 195 |

| Li               | ${ m st}$ of | Publications                               | 233 |

### Abstract

#### **English version**

The number of smart devices for the Internet of Things (IoT) is rapidly growing, and by 2025 almost 80 ZB of data per year will be generated by IoT devices alone, challenging the current cloud computing infrastructure. Thus, a shift to the edge computing paradigm, in which data are processed near their sources, is critical, but its implementation requires new energy efficient computing hardware. The approaching downscaling limit of transistor size implies the need for new nanoscale technologies and a departure from the conventional von Neumann architecture. Also, in-hardware security primitives need to be introduced at the silicon level.

Among the possible technologies, emerging non-volatile memories (eN-VMs) are very promising and enable the realization of in-memory computing paradigms, in which computation is executed directly inside the memory, therefore bypassing the slow and energy inefficient data exchange over a communication bus, i.e., the main bottleneck of von Neumann architectures. However, the intrinsic stochastic nature of eNVMs presents several challenges which can impact the circuit functionality and reliability. On the other hand, it can be exploited to implement hardware-level security primitives such as True Random Number Generators (TRNGs) and Physical Unclonable Functions (PUF). Thus, appropriate design tools and methodologies are needed to

help circuit designers exploit eNVMs strengths while consciously addressing their limitations.

The optimization of circuit simulation tools and the development of appropriate methodologies to analyze and improve innovative circuits based on eN-VMs for computing and security applications is the goal of this PhD thesis. Specifically, a physics-based Resistive RAM (RRAM) compact model (Uni-MORE compact model), was developed starting from a prototypical existing version, and refined to include self-consistently the role of variability, thermal effects, and Random Telegraph Noise (RTN). In addition, an automated parameter extraction procedure is developed and included. Such procedure requires only the results of a few experiments that are commonly employed in the device characterization, and was validated both experimentally and on three RRAM technologies from the literature. The procedure allows quick model calibration and helps in determining the strengths and weaknesses of different RRAM technologies for a dependable device-circuit co-optimization. The calibrated compact model is used to analyze the performance and reliability trade-offs of different in-memory computing paradigms. Specifically, the results of circuits simulations of state-of-the-art Logic-in-Memory (LiM) circuits based on the material implication (IMPLY) logic and RRAM technology enabled the development of design procedures for optimizing their reliability, which are here discussed. Also, a novel smart IMPLY (SIMPLY) LiM architecture, which solves the circuit reliability issues of conventional IMPLY architectures, is proposed. The reliability and performances of the SIMPLY architecture were thoroughly investigated considering different RRAM technologies and benchmarked on complex operations. Furthermore, the results of the study on RRAM-based low-bit precision neural networks (NNs) analog hardware accelerators are presented, highlighting specific reliability and

performance trade-offs. Also, a novel hybrid in-memory computing hardware accelerator in which both SIMPLY and the analog vector matrix multiplication framework coexist on the same memory crossbar array is demonstrated. Finally, challenges and opportunities for RTN-based TRNG circuits are presented. Specifically, the impact of different materials and fabrication processes on the quality of the generated RTN signal and consequently on the output of a TRNG circuit implementation is discussed.

#### Italian version

L'enorme mole di dati prodotta dai dispositivi per l'Internet of Things richiede una trasformazione dell'attuale infrastruttura di cloud computing: lo spostamento di parte dell'elaborazione dove i dati vengono generati (edge computing). Per attuare questo cambio di paradigma, lo sviluppo di nuove soluzioni hardware più efficienti per l'elaborazione dei dati è fondamentale. Inoltre, il sopraggiungere del limite fisico di miniaturizzazione dei transistor implica la necessità di sviluppare nuovi nanodispositivi e nuove architetture di calcolo, che si scostano dalla tradizionale architettura di von Neumann. Oltretutto, i sempre più stringenti requisiti di sicurezza richiedono l'introduzione di primitive di sicurezza direttamente a livello hardware. In questo panorama, le tecnologie emergenti nell'ambito delle memorie non volatili (eNVM) rappresentano una soluzione promettente e permettono l'implementazione di paradigmi di elaborazione in memoria, che eliminano il principale collo di bottiglia delle architetture di von Neumann, ovvero l'inefficiente scambio di dati tra la memoria e l'unità di elaborazione. Tuttavia, la natura stocastica dei dispositivi eNVM influisce sulla funzionalità e sull'affidabilità di questi circuiti, complicandone la progettazione. D'altra parte, questi fenomeni stocastici possono essere sfruttati per implementare primitive di sicurezza a

livello hardware. Pertanto, per sfruttare le potenzialità delle eNVM sono fondamentali nuovi strumenti e nuove metodologie di progettazione. L'obiettivo di questa tesi di dottorato è l'ottimizzazione di strumenti per la simulazione circuitale e lo sviluppo di metodologie appropriate per l'analisi ed il miglioramento di circuiti innovativi basati sulle eNVM per applicazioni di elaborazione e sicurezza. In particolare, viene proposto un modello compatto di RAM resistiva (RRAM) (modello compatto UniMORE), sviluppato a partire da una versione prototipale esistente e perfezionato per includere in modo autoconsistente il ruolo della variabilità, degli effetti termici e del Random Telegraph Noise (RTN). Inoltre, viene descritta una procedura di estrazione dei parametri automatica che richiede solo i risultati di alcuni esperimenti comunemente impiegati durante la caratterizzazione dei dispositivi, e che è stata validata sia sperimentalmente che su tre tecnologie RRAM dalla letteratura. Grazie al modello compatto calibrato, vengono analizzate le prestazioni e l'affidabilità circuitale di diversi paradigmi di elaborazione in memoria. In particolare, mediante simulazioni circuitali di circuiti Logic-in-Memory (LiM) basati sulla logica di implicazione materiale (IMPLY) e sulla tecnologia RRAM, sono state sviluppate procedure di progettazione volte a massimizzarne l'affidabilità circuitale. Inoltre, viene presentata una nuova architettura LiM chiamata smart IMPLY (SIMPLY), che risolve i problemi di affidabilità comunemente presenti nei circuiti convenzionali. L'affidabilità e le prestazioni dell'architettura SIMPLY sono state studiate dettagliatamente considerando diverse tecnologie RRAM e l'esecuzione di operazioni complesse. Inoltre, tramite simulazioni circuitali sono stati analizzati acceleratori hardware di reti neurali a bassa precisione, evidenziandone i compromessi esistenti tra affidabilità ed elevate prestazioni. Viene anche presentato un nuovo acceleratore hardware che combina sullo stesso array di memoria due diversi

paradigmi di elaborazione in memoria, ovvero SIMPLY e l'accelerazione in analogico del prodotto matrice vettore. Infine, vengono discusse le sfide e le opportunità per i circuiti True Random Number Generators basati su RTN, mediante una analisi approfondita dell'impatto che differenti materiali e processi produttivi hanno sia sulla qualità del segnale RTN generato che sulle prestazioni di una realizzazione circuitale di TRNG.

## Chapter 1

Resistive memory devices for the future of computing and security applications

# 1.1 Ultra-low power computing and security functions

#### 1.1.1 Beyond Moore's law

From its invention in 1947 by the researchers at Bell Labs, the transistor has completely revolutionized many aspects of our life and promoted an exponential growth of the electronic industry. The diffusion of electronic devices and computing capabilities has corresponded to a rapid increase in the amount of produced data accompanied by increasing demand for more computing power. Scaling the size of devices corresponded to an increase of the number of transistors that could be fabricated in a chip, which doubled every two years according to Moore's law. This increasing device density together with

an increase of the clock frequency led to an increase in computing performance. Thanks to this strategy, the increasing demand for computing power was satisfied up until the early 2000s, when the increasing power density of transistors at smaller sizes required limiting the clock frequency to avoid overheating the chips. Still, the demand for increased computing power has never stopped growing highlighting the need for innovations both at the device and circuit architecture level. In addition, new technologies such as the Internet of Things (IoT) are expected to exponentially grow in the next few years. The use of low-power smart devices for the IoT alone is expected to produce almost 80 ZB of data by 2025 [1], challenging the conventional cloud computing infrastructure and demanding a shift to the edge computing paradigm. In edge computing, computations are performed in close proximity to where the data is generated, thus reducing the burden of inefficient data transmissions, improving user security, and reducing latency. However, to sustain such a paradigm shift ultra-low-power computing solutions are required. Therefore, to achieve the goal of ultra-low-power computing hardware solutions efforts in the scientific community and in the industry have been directed towards the research of new nanotechnology devices and computing architectures which depart from the traditional von Neumann architecture.

#### 1.1.2 In-memory computing

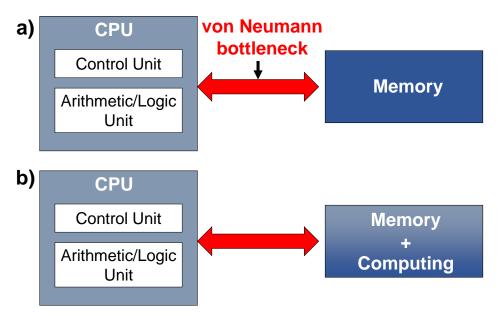

In the conventional von Neumann architecture, the processing (i.e., CPU) and the storage of the data (i.e., memory) are separated and connected by a communication bus, see Fig. 1.1a. This separation is the source of high time and energy inefficiencies, leading to the common problem known as the von Neumann bottleneck (VNB) [2]. In fact, while the CPU is extremely efficient and fast in executing operations, the memory access and data transfer over

Figure 1.1: a) Sketch of the von Neumann architecture where the von Neumann Bottleneck is highlighted. b) Novel non-von Neumann architecture, which enables to execute operations directly in-memory, bypassing the von Neumann Bottleneck.

buses require orders of magnitudes higher energies and times [3]. Also, the growing adoption of machine learning and deep learning algorithms that are commonly characterized by data-intensive operations further exacerbates this issue.

In the strive for energy-efficient computing schemes, one of the most efficient solutions comes from nature, i.e., the human brain, which dissipates around 20W while performing 10<sup>15</sup> calculations per second [4], [5]. Differently from the von Neumann architecture, in the brain processing and memory are co-located and take place in neurons and synapses. Such high energy efficiency is not the result of extremely fast and accurate neurons and synapses but rather of their dense interconnection. Thus, by taking inspiration from nature efforts have been directed towards the development of solutions bringing the computation and the storage closer to each other, realizing in-memory

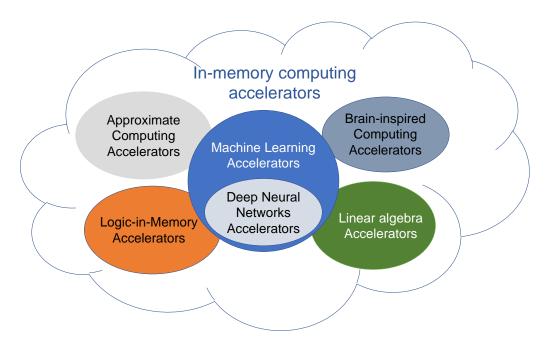

**Figure 1.2:** Different categories of in-memory computing hardware accelerators. Some overlap between different computing paradigms exist.

computing architectures [6]–[10], where the computation takes place inside the memory using the memory element both as a storing and as a computing element, see Fig. 1.1b.

These new in-memory computing solutions can be used to realize hardware accelerators and thus speed up the execution of specific tasks or operations. Different in-memory accelerators have been theorized in the last decade, which can be divided into the following five major groups, which are shown in Fig. 1.2. Specifically, Logic-in-memory (LiM) accelerators enable the efficient execution of logic operations directly in-memory [10]–[13]. Some applications may not require exact precision of the computations and tolerate higher error rates. Thus, such applications may benefit from the adoption of accelerators for the approximate computing paradigm [14], [15] in which high efficiency is achieved by trading off with lower accuracy of the compu-

tation. The rapid adoption of deep learning has prompted several solutions for the in-memory acceleration of deep neural networks (DNNs) [3], [7], [16]. Also, accelerators for linear algebra problems are being studied [9], [17], [18]. Finally, accelerators for biologically inspired computing paradigms such as spiking neural networks (SNNs), which mimic the neural networks in brains, composed of neurons and synapses, are being studied [4], [6], [8], [19], [20].

While some in-memory solutions exploiting well-known memory technologies (e.g., FLASH, DRAM, SRAM) have been proposed [21]–[25], new emerging nonvolatile memory (eNVM) technologies are currently the frontrunners for enabling the diffused adoption of these new computing paradigms, thanks to their low-cost, high-density, high switching speed, and the potential possibility of enabling the multi-bit storage on a single device. Although some prototypes have been successfully demonstrated [26]–[28], this field is still in its infancy. Before the diffused commercialization of these hardware accelerators a lot of research directed to improving the memory technology, the circuit architectures, and the development of new software primitives, still needs to be done.

#### 1.1.3 Emerging nonvolatile memory technologies

Several new nonvolatile memory technologies enabled by innovations in the material sciences have been researched in the last decades, motivated by the need to fill a performance gap currently present in the memory hierarchy of computers. Currently, a performance gap exists [29] between the nonvolatile memory, commonly implemented with the relatively cheap and high capacity NAND flash technology, and the DRAM which provides the nonvolatile storage of information and higher speeds however at higher costs. Although eNVM technologies cannot compete in terms of cost per bit with NAND

flash and terms of speed with DRAM, they provide a good balance between the two, and thus were identified as a solution for implementing the storage class memory [30]–[32]. However, it was soon realized that such new eNVMs could enable the implementation of energy-efficient in-memory computing accelerators [3], [7], [9], [11], [26], [33].

In fact, the group of eNVM technologies commonly includes different two and three terminals nonvolatile memory devices, which by exploiting different physical mechanisms can be programmed to store a single bit or even multiple bits in a single device. These technologies include resistive random access memories (RRAM) such as metal-oxide (OxRAM) [34], [35] or conductivebridging RAM (CBRAM) [36], [37], Phase Change Memories (PCM) which are based on chalcogenide materials [38]–[40], Ferroelectric RAM (FeRAM), Ferroelectric FET (FeFET) [41], Ferroelectric Tunnel Junction (FTJ) devices which exploit the properties of ferroelectric materials [39], [42], Spin-Transfer Torque (STT-MTJ) [39], [43] and Spin-Orbit Torque (SOT-MTJ) [44]-[48] magnetic RAM devices which employ ferromagnetic materials. In general, two-terminal devices are built by introducing a layer of a material (usually an insulator) with specific properties between two metal electrodes realizing a metal-insulator-metal (MIM) structure. Using electrical pulses it is possible to change the properties of the insulating material which produces a variation of the equivalent conductivity of the device. Thus, a bit of information can be stored with two different conductivity values, while for storing multiple bits in a single device, its conductance needs to be reliably programmed into more than two distinguishable values. Three terminal devices are commonly built as FET devices where specific materials are inserted between the gate electrode and the transistor channel. Thus, varying the properties of specific materials inserted under the gate electrode modulates the threshold voltage

of the FET device and thus the conductance between the source and drain terminals for a specific gate voltage.

For the fabrication of such eNVM devices, materials compatible with the back end of line (BEOL) fabrication processes are commonly employed, enabling the vertical exploitation of the integrated circuit, potentially stacking the memory array on top of the control logic that is fabricated in the front end of line (FEOL). Very high memory densities are commonly achieved. Specifically, two-terminal devices can be used to build 2D crossbar arrays where a memory device is placed at the intersection of each vertical and horizontal line. More crossbar arrays can be stacked on top of each other to increase the memory density (i.e., number of bits stored per unit area), however, 3D vertical arrays are more cost-effective but still only implementations based on resistive memories have currently been demonstrated [35].

A common characteristic of eNVM technologies is their intrinsic stochasticity which is introduced by defects caused by fabrication processes and by the intrinsic device behavior, which lead to several nonideal effects such as the resistance drift problem shown by PCM devices which determines a progressive increase of the device resistance or the cycle-to-cycle (C2C) and device-to-device (D2D) variation shown by resistive memory devices which causes the random distribution of their resistance. Thus, although some computing approaches such as the DNN, SNN, and linear algebra solver may benefit from the multi-bit storage, currently storing more than one bit in a single device is still challenging [35], [49].

Also, eNVM technologies are characterized by different performance and characteristics [38], [41], [47]–[51]. As shown in Table 1.1, although all the eNVM reported providing faster programming and reading speed and longer endurance compared to NAND flash memory technologies, still none of them

**Table 1.1:** Comparison of the performance of different eNVM technologies . Data from [38], [41], [47]-[51]

|                    | Flash                   | PCM                     | RRAM                     | STT-MTJ                  | SOT-MTJ                  | FeFET      |

|--------------------|-------------------------|-------------------------|--------------------------|--------------------------|--------------------------|------------|

| Endurance          | $< 10^{5}$              | $10^8 - 10^{11}$        | $10^6 - 10^{12}$         | $> 10^{15}$              | $> 10^{15}$              | $< 10^{8}$ |

| Retention          | $> 10 \mathrm{y}$       | >10 $y$                 | >10 $y$                  | >10y                     | >10y                     | >10 $y$    |

| ION/IOFF           | $> 10^8$                | $> 10^4$                | $> 10^{3}$               | >2                       | >2                       | $> 10^8$   |

| Programming energy | $\approx 10 \text{ fJ}$ | $\approx 10 \text{ pJ}$ | $\approx 100 \text{ fJ}$ | $\approx 100 \text{ fJ}$ | $\approx 100 \text{ fJ}$ | < 10 fJ    |

| 3D integration     | yes                     | yes                     | yes                      | no                       | yes                      | yes        |

| Write speed        | <10 ms                  | <100 ns                 | <10 ns                   | <5 ns                    | <1 ns                    | <10 ns     |

| Read speed         | $< 10~\mu s$            | <10 ns                  | <10 ns                   | <10 ns                   | <10 ns                   | <10 ns     |

is able to meet all the ideally required performance criteria for every inmemory computing architecture [49]. In fact, an ideal memory device would require very high endurance (i.e.,  $> 10^{17}$ ), >10 years retention, low-voltage (i.e., <1 V) operation, large memory window (i.e.,  $I_{ON}/I_{OFF} > 10^2$ ), lowprogramming energy (1 fJ/bit), fast programming speed (i.e., <10 ns), and 3D integration. Thus, although improvements are still required from the technology perspective, in the short-term circuit designers should identify the most suitable technology for a specific application while compensating its weaknesses during the circuit design. Thus, device-circuit co-optimization strategies need to be developed together with fast and accurate compact models.

#### 1.1.4 Hardware security building blocks

Among the requirements of IoT and edge computing, security together with energy efficiency is the most important. In fact, IoT systems need to be resilient to possible malicious attacks which aim to get access to private (e.g., interfere with bank transactions) and sensitive information or mine the reliability of a system. For instance, malicious attacks can come in the form

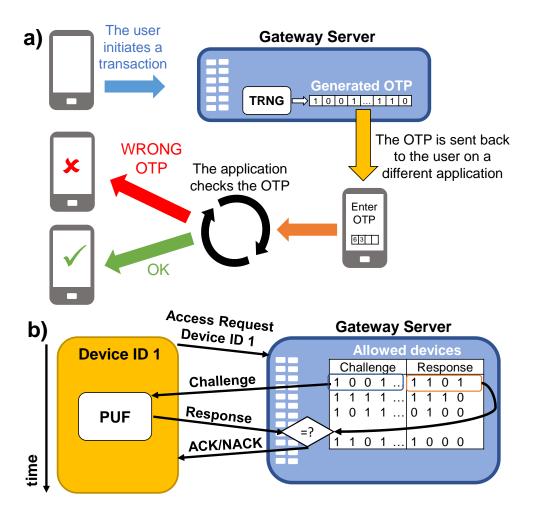

of physical or network attacks [52]. In IoT devices or systems, these attackable sources need to be protected by introducing appropriate security primitives. Although software-based security solutions have been developed, it was demonstrated that hardware-based security solutions are far more secure [53]–[55]. Still, even with state-of-the-art integrated circuit technologies, past cyber-attacks (e.g., the row hammer attack [56]), by succeeding, have demonstrated possible limitations of current solutions. Also, the adoption of new nanotechnologies, such as eNVM, requires the development of new hardware security primitives. Thanks to their intrinsic stochasticity, eNMV technologies offer new opportunities for reaching the high-security targets required by new systems, which however still need to be thoroughly investigated. In general, security solutions, such as the encryption of messages, user authentication to a system, require the generation of random private keys. In this regard, the stochasticity displayed by eNVM devices can be used as an entropy source. Different hardware security primitives based on eNVM have been proposed in the literature [54], [57]–[62]. Specifically, true random numbers generators are used to generate random bit streams which can be used to build random keys used for encrypting messages [52], [55], [58], and an example application is illustrated in Fig. 1.3a. Also, the Physical Unclonable Function (PUF) is a promising hardware security primitive and can be used in authentication applications [58], [62]. A PUF typically exploits the randomness introduced as a side effect during manufacturing [61] to create random challenge-response pairs that are unique for each fabricated chip, see Fig. 1.3b where an example application is described. Finally, machine learning systems based on eNVM have been proposed as a possible hardware solution that could help in identifying anomalies (i.e., possible attacks) during the device operation [52].

Figure 1.3: a) Example application of a TRNG circuit. A TRNG generates a OTP, which is used to authenticate a transaction in a two-factor authentication system. b) Use case application example of a PUF circuit, for authenticating a device in a system. The device sends an access request to the server, which responds by sending the challenge specific to the device ID requesting the access. In the device, the challenge is input to the PUF which outputs the response that is sent back to the server which compares it with the one stored in its internal memory, and grants or denies the access.

#### 1.1.5 The focus of this thesis

Although a lot of research activity has been directed toward the development of novel solutions for the IoT by exploiting eNVM technologies, enabling their rapid diffusion still requires significant research efforts.

The work presented in this thesis addresses the need for ultra-low-power and secure computing solutions by studying and developing computing and security schemes exploiting the RRAM technology. Among the in-memory computing solutions described in Section 1.1.2, LiM and DNN hardware accelerator are analyzed and developed, while novel True Random Number Generator (TRNG) circuits are discussed as a promising hardware security primitive.

#### 1.2 Resistive Random Access Memories

Among the different eNVM technologies, RRAM technologies are one of the most promising thanks to their simple fabrication, high switching speed, low programming energy, 3D integration, and compatibility with CMOS processes. An RRAM device consists of a two-terminal MIM structure. When considering the binary memory case as an example, the resistance of the device can be switched between a high resistive state (HRS) and a low resistive state (LRS) which are commonly associated with "0" and "1" logic values. When no external voltage is applied to the RRAM device it retains the stored value, which can be read by applying a small read voltage pulse across its terminals. Depending on the materials used during the fabrication of the MIM structure, different switching mechanisms can occur, such as the valence change mechanism (VCM) [34] and the electrochemical conduction mechanism (ECM) [36], which result in the OxRAM and CBRAM categories.

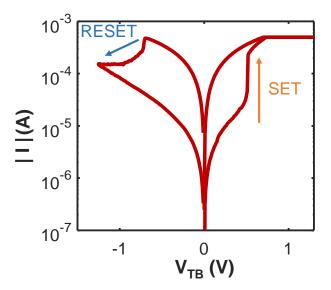

**Figure 1.4:** Example of the I-V characteristic of a bipolar RRAM device. The set and reset events are highlighted.  $V_{TB}$  is the voltage applied across the top and bottom electrodes.

In this thesis, we focus on the metal-oxide-based RRAM cell exhibiting filamentary switching.

#### 1.2.1 Metal Oxide MIM devices

The first experiments on MIM structures date more than 40 years back, when it was observed that oxides that are nominally insulators can transition into a conductive state as a consequence of an abrupt switching event [63], [64]. However, the first experiments did not result in a sufficiently reliable resistive switching and thus could not be used for memory application. A resurgent and intensified research activity regarding RRAMs started after the demonstration by Samsung of NiO-based memory cells in 2004 [65]. By then several works have investigated the effect of different metal-oxide material combinations [34]. In fact, the resistive switching behavior depends on the oxide material, the used metal electrodes, and their interfacial properties [34].

In general, resistive switching is achieved by applying across the MIM electrodes appropriate voltages. To switch a device from a LRS to a HRS (i.e., reset operation) a  $V_{RESET}$  voltage is delivered to the device, while the opposite transition (i.e., set operation) requires the use of a  $V_{SET}$  voltage. Depending on the polarity of  $V_{SET}$  and  $V_{RESET}$ , devices can be divided in unipolar and bipolar switching categories. In unipolar switching,  $V_{SET}$  and  $V_{RESET}$  have the same polarity and the execution of a reset or set operation depend on the amplitude of the applied voltage. In bipolar switching,  $V_{SET}$  is positive while  $V_{RESET}$  is negative, resulting in a butterfly shaped IV relation, as shown in Fig 1.4. Also, by modulating the amplitude of the reset voltage pulse, it is possible to program a device in different nominal HRS values. In this thesis we consider bipolar switching devices.

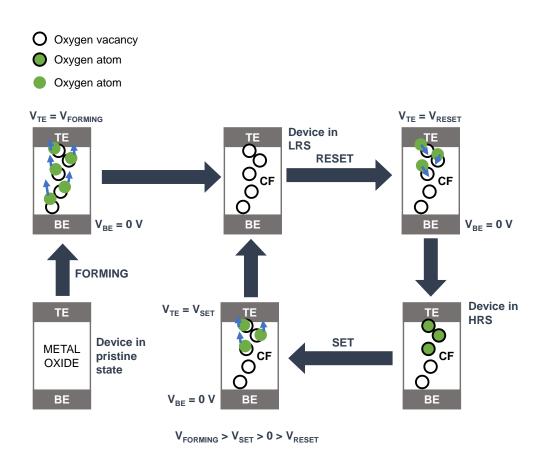

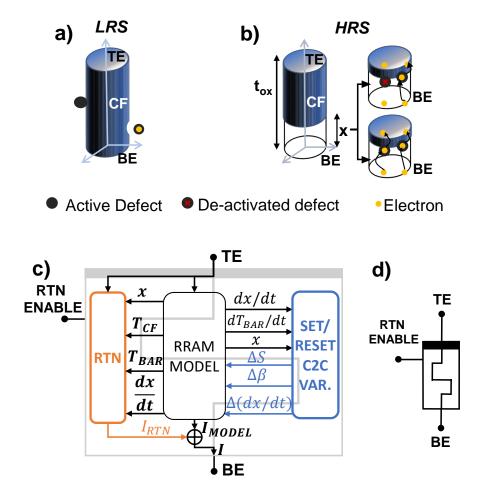

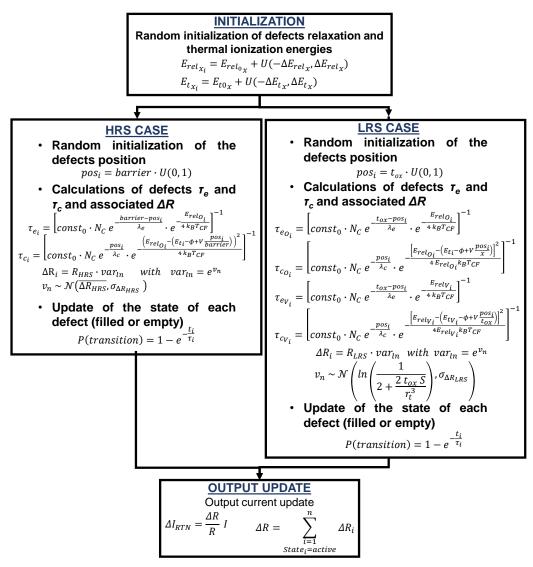

From a device physics perspective, the switching mechanism sketched in Fig. 1.5 is associated with the formation and dissolution of conductive filament (CF). To initiate resistive switching, fresh devices undergo a forming process, which corresponds to a soft breakdown of the dielectric. As a result of the application of high electric fields, oxygen ions drift to the top electrode (TE) interface where are accumulated [34]. After the forming step a CF of oxygen vacancies is created and the device is in LRS.

When performing a reset operation, the oxygen ions migrate back to the dielectric where they recombine with the oxygen vacancies, thus partially dissolving the CF and restoring the HRS [34].

The set operation, is similar to the forming process, however it requires lower voltages. Also, in OxRAM technologies the forming and the set processes are commonly abrupt, thus requiring the introduction of a current compliance. The value of the current compliance determines the size of the CF filament and thus the LRS resistance value.

Figure 1.5: Sketch representation of the switching processes occurring in RRAM devices, which is represented as a dielectric material stacked between a metallic top and bottom electrodes (i.e., TE and BE, respectively). The forming step results in the creation of a CF due to a soft dielectric breakdown that causes oxygen ions to drift to the TE. During reset, the oxygen ions recombine with the vacancies resulting in a HRS. During set, similarly to the forming step, results in the oxygen ions drift to the TE and the CF restoration. Figure adapted from [34].

Charge transport in the device has been demonstrated to be mainly assisted by oxygen vacancies [34], [66]–[68]. Specifically, in devices in LRS an Ohmic-like drift conduction through the defect rich CF is observed, while in HRS the current conduction is believed to be assisted by trap assisted tunneling (TAT) through the oxygen vacancies in the oxide [34], [66]–[68].

#### 1.2.2 Stochastic behavior of RRAM devices

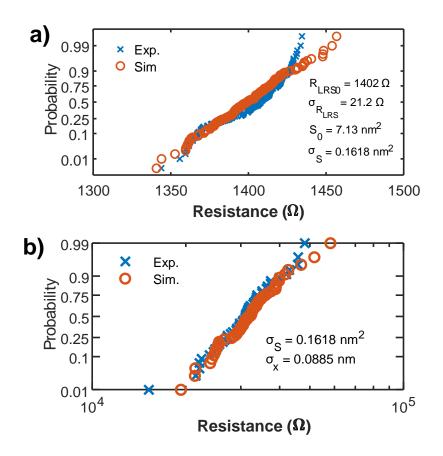

RRAM devices present different challenges for circuit designers. In fact, many nonideal effects influence the device behavior and potentially result in reliability issues if not appropriately considered during the design phase. The main challenges, currently come from variability and random telegraph noise (RTN), which induce random resistance variations which currently hinder the reliable multi-bit storage [69], [70].

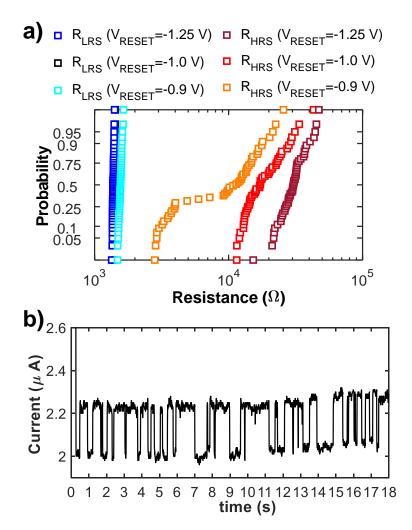

Although D2D variations could be reduced by improving the fabrication processes, C2C variations are intrinsic to the device operation and result in randomly distributed LRS and HRS resistances [70]. In fact, the diffusion and recombination of oxygen ions during reset and the bond breaking during a set are partially stochastic processes [49], [69]. Thus, the shape and the number of oxygen vacancies composing the CF change from C2C, leading to a normally distributed LRS resistance [69]. Lower current compliance values reduce the size of the CF, thus making the charge transport more affected by variations of the number of vacancies building the CF, increasing the standard deviation of the LRS resistance distribution [49]. Also, when a device is reset, the position and number of vacancies in the oxide layer assisting the TAT charge transport change from C2C, leading to log-normally distributed HRS resistances [71]. An example is shown in Fig. 1.6a, where a considerable overlap between HRS distributions for different reset voltages

Figure 1.6: a) Example of the LRS and HRS distributions resulting from programming an RRAM device with different reset voltages ( $V_{RESET} = -0.9V, -1.0V, -1.25V$ ). Due to C2C variations, a considerable overlap exists between the HRS distributions. b) Example of a two-level RTN signal from an RRAM device.

is clearly visible. Closed-loop programming algorithms, such as write and verify programming schemes [72], [73], can be used to limit the spread of the resistance distributions however at the cost of increased complexity and area on the chip.

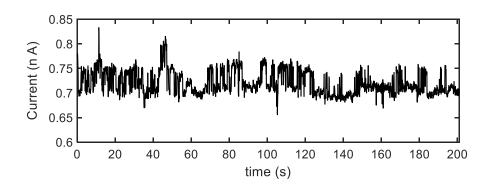

RTN introduces unpredictable current fluctuations between two (i.e., two-level RTN) or more (i.e., multi-level RTN) discrete levels, which negatively impact the circuit reliability, especially during device read operations, because it reduces the available readout margin [69], [71]. For a device in HRS, RTN is commonly linked to the temporary activation and de-activation of oxygen vacancies that normally assist the TAT charge transport, by the effect of charge trapping and de-trapping in slower oxygen ions defects not assisting charge transport, that are located in their proximity. In LRS, RTN current fluctuations are connected to the trapping and de-trapping of charges in defects nearby the CF which perturb the potential in their surroundings, partially screening the charge transport in the CF due to the Coulomb interaction [74]. An example of a two-level RTN current signal is shown in Fig. 1.6b.

In general, all these stochastic effects together with other devices' non-idealities (e.g., conduction nonlinearity, self-heating) need to be taken into account during the circuit design phase to achieve reliable circuits operation [75], [76]. Thus, physics-based compact models capable of reproducing such effects are fundamental tools to enable reliable circuit simulations.

# 1.3 In-memory computing with state-of-the-art RRAM devices

Different in-memory computing hardware accelerators based on RRAM devices have been proposed in the literature. As discussed in the previous sections, variability and RTN limit the number of bits that can be reliably stored in a single device, thus making the practical realization of some in-memory computing paradigms very challenging and hindering their commercialization in the near future. For instance, although the in-memory training of DNNs would considerably reduce the energy needed to train the large number of parameters of DNNs it would require at least 6 bits (i.e., 64 discrete resistance levels) to be stored on a single RRAM device [28]. Thus, in this thesis in-memory computing paradigms which can exploit current state-of-the-art RRAM technologies are discussed. Specifically, LiM and DNN inference hardware accelerators.

#### 1.3.1 Logic-in-Memory

LiM computing architectures are currently being researched as a solution for implementing reconfigurable hardware accelerators which enable the execution of logic operations using the memory element both for storage and computing. Although, some non in-memory implementations of hybrid CMOS-eNVM approaches in which logic gates combining both technologies have been theorized [77], LiM technologies represent a more promising solution, since they circumvent the VNB and offer intrinsic parallelism and reconfigurability, enabling the implementation of single instruction multiple data (SIMD) computing architectures.

Different LiM solutions based on RRAM devices, or memristor in general,

have been proposed [10]–[12], [26], [78]–[80], and some common features are here described. Specifically, a first difference with respect to conventional digital logic gates is the use of devices' nonvolatile resistances as the inputs of computations. Different LiM solutions usually differ for their set of core operations, which commonly comprise a complete logic group thus enabling the computation of any logic operation. For instance, material implication (IMPLY)- based architectures execute IMPLY and FALSE operations [10], [26], [81], the Memristor aided logic (MAGIC) [11] the NOR and NOT operations, while the scouting logic [79], [80] AND, OR, NOT logic operations. Therefore, while more complex logic functions are usually implemented by using more transistors in conventional CMOS gates, in LiM approaches it equates to the execution of longer sequences of core operations (i.e., increased latency in the computation). Depending on the type of scheme adopted for the driving signals, LiM computing paradigms can be divided into stateful and non-stateful.

#### Stateful LiM paradigms

LiM architectures are stateful when both the inputs and outputs of the computation are encoded in the non-volatile resistance of RRAM devices. This category includes the IMPLY-based and MAGIC architectures. In general, in stateful computing paradigms appropriate voltage pulses are delivered to multiple memory devices encoding the inputs and output of the computation. Depending on the resistive state of the input devices, the output changes state according to the truth table of the specific core operation that is implemented. Although these approaches, represent an interesting opportunity which does not require the use of additional control logic, the concurrent execution of the computing and the conditional programming steps leads to

complex design trade offs and reliability issues [10], [79], [82]. Such reliability issues can be easily overlooked when performing circuit simulations with simplified device compact models leading to unreliable circuits [82].

#### Non-stateful LiM paradigms

LiM architectures are non-stateful when the inputs of the logic operation are encoded with devices' resistive states while their outputs with voltages. Also, the peripheral circuitry of the memory array is used in the computations of logic operations. An example is the scouting logic [80], where the output of a voltage divider between the inputs RRAMs is compared with multiple thresholds. However, the effects of C2C and D2D variability, and RTN, result in considerable overlap between the voltage distributions for different inputs configurations (e.g., it is not possible to distinguish the case when both inputs are in LRS or when only one is in LRS), resulting in unreliable circuit operation and high bit error rates (BERs). The enhanced scouting logic [79] was introduced to improve the circuit reliability however at the cost of a much larger circuit area by employing 2T1R devices arrays, limiting their competitiveness.

## 1.3.2 Analog computing with memory arrays for deep neural networks

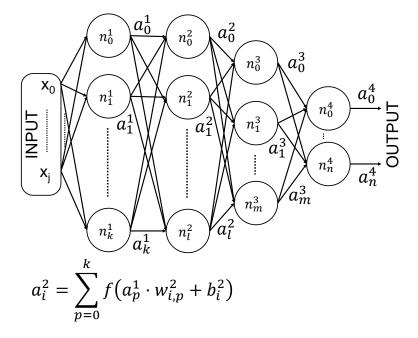

DNNs require the execution of a few operations that are however repeated on multiple data. Considering the simple multi-layer perceptron neural network shown in Fig. 1.7, each layer of the network is composed of several artificial neurons each characterized by different parameters (i.e., the weights multiplying the inputs and a bias term) that are learned during training. When performing an inference task, each neuron computes the sum of the

**Figure 1.7:** Structure of a multilayer perceptron neural network with three hidden layer. The operations computed by each neuron are reported.

products between its inputs and its weights (i.e., the multiply and accumulate operation (MAC)), and a bias term is added to the result. Finally, a nonlinear function computes the output activation of the neuron. Since most of the common networks topologies are composed of several layers with many neurons, the MAC operations use most of the computing resources and memory bandwidth due to the need of retrieving the neurons' weights. Thus, hardware accelerators based on RRAM devices for accelerating the MAC operation are being intensively studied [7], [16], [83], [84]. Indeed, the in-memory computation of the MAC operations would provide considerable energy efficiency improvement with respect to conventional solutions.

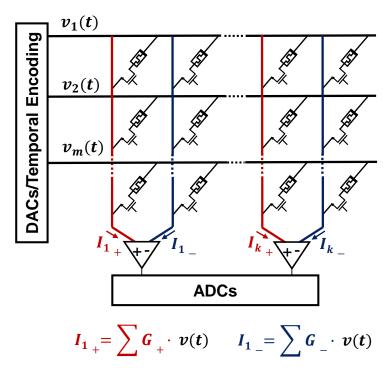

As shown in Fig. 1.8, by mapping the weights of each neuron to resistance levels of RRAM devices in the columns of a crossbar array, and encoding the input activation in the row voltages of the crossbar, the results of the MAC operation is computed in a single step for each neuron, by exploiting the

Figure 1.8: Representation of the core structure of an in-memory accelerator of the MAC operations based on 1T1R memory arrays. Each weight of a layer of the network is mapped onto the resistance of two devices located on the same row and adjacent columns (red and blue columns), enabling to encode both positive and negative weights. The row decoder, equipped with digital to analog converters (DACs), delivers the input activations as voltages to the rows of the memory array. The result of the MAC operation is computed as the difference between the currents flowing in each pair of columns (each pair of red and blue columns) which is digitized with ADCs.

Kirchhoff's current law and the Ohm's law. The result of the MAC operation is encoded in the current flowing in each column. Such currents are commonly converted to voltages with transimpedence amplifiers and digitized with analog to digital converters (ADCs) [7], [16], [83], [84]. Also, to map positive and negative weights to positive resistances, two devices are commonly used to encode both positive and negative weights, as shown in Fig. 1.8.

Due to the current limitation of the multi-bit storage, DNN approaches that employ a reduced number of bits during inference should be preferred. For instance, binarized neural networks (BNN) [85] have been shown to provide high accuracy despite the use of a single bit to represent weights and activations. Also, slightly increasing the number of bits encoding the activations, realizing low-bit precision neural networks (LBPNN) have been shown to result only in a slight accuracy drop compared to full precision networks. Some examples of RRAM-based BNN and LBPNN accelerators have been proposed in the literature [28], [57], [86], [87], however, still, a clear analysis of the circuit reliability in the presence of RTN and variability is missing, together with a clear understanding of the circuit design trade-offs.

These are parts of the focus of this thesis, and the results of the circuit reliability analysis of a LBPNN implementation enabled by the UniMORE RRAM physics-based compact model are discussed in Chapter 3 together with appropriate design strategies.

## 1.4 True Random Number generator circuits

As mentioned in the previous sections, TRNG circuits are a fundamental hardware security primitive which is used to generate bitstreams of random

bits. For instance, TRNG circuits are used for the generation of temporary one-time passwords (OTP) that are used when strong authentication algorithms are needed [88]. Ideally, a TRNG circuit should output random bits with i) high entropy, ii) sufficiently high throughput, iii) consuming low energy, iv) providing high security to potential malicious attacks.

To achieve these goals, different RRAM-based TRNG circuits have been proposed in the literature, each exploiting different stochastic phenomena that are intrinsic to RRAM devices. Specifically [55]:

- The probability of a resistive state transition after the application of an appropriate bias voltage

- The time required to switch a device between two resistive states

- C2C resistance variations

- RTN current fluctuations

Thus, C2C variations and RTN represent the two main entropy sources. In fact, by programming a device with voltage pulses with different duration and amplitude, it was shown that for some pulse duration and amplitude pairs a 50% of chance of switching a device from a HRS to a LRS can be achieved [89]. Thus, a random bit can be obtained by first performing a device set, followed by a probabilistic reset operation, after which the resistive state of the device is read with a small read voltage pulse.

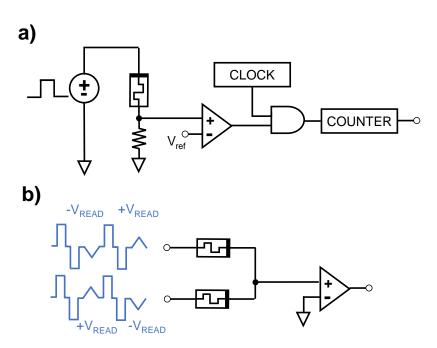

Also, the time required to switch a device changes from C2C, and it can be collected with the circuit in Fig. 1.9a presented by Jiang et al. [90]. In this circuit, a digital counter measures the time required for a device to switch from a HRS to a LRS after the application of a programming pulse.

The circuit in Fig. 1.9b, shows the TRNG implementation from [91] which exploits the resistance variations from C2C. Specifically, the two devices are

Figure 1.9: a) Example of a circuit from [90] extracting the time required to reset a device. After resetting the counter a reset pulse is delivered to the RRAM device. The counter starts to count with an appropriate clock frequency. A comparator detects when the resistance of the device passes a threshold, stopping the counter. b) Example of a TRNG circuit from [91] exploiting the C2C resistance variations of two RRAM devices as an entropy source. After resetting the devices two complementary read pulses are delivered to the two devices. By inverting the polarity at each read cycle, potential bias issue are prevented.

programmed independently in the same resistive state, and a random bit is generated by applying two complementary voltage pulses simultaneously to the two devices and comparing the common node with 0 V. Thus, a "0" logic bit is output when the resistance of the device that is read with a negative voltage is lower than that of the other device, otherwise, "1" logic bit is output.

Although these approaches can result in TRNG circuits with relatively high throughput, they are based on the switching of RRAM devices, thus potentially incurring into reliability issues due to the limited device endurance. Also, the switching of a device requires more energy compared to a device read operation.

Thus, RTN-based TRNG circuits, despite the lower achievable throughput which is limited by the defects capture and emission times, are a promising and more energy-efficient, low-cost solution that does not incur endurance issues since they do not require the switching of the RRAM devices. Although, a few examples of RTN-based circuit architectures using the RTN signal have been proposed [92]–[96], a clear understanding of the impact of material, and fabrication processes on the quality of the RTN signal are still missing. Ensuring a high-quality RTN signal is fundamental for achieving reliable and robust TRNG circuits. Conversely, identifying possible limitations of RTN signals produced by a specific technology could promote the activity of circuit designers to devise appropriate compensation strategies at the circuit level. Adding this piece of information to the literature is one of the objectives of this thesis and it is discussed in Chapter 4.

#### 1.5 Thesis structure

In this thesis we advance the state-of-the-art, addressing several problems that are currently present in the field of ultra-low-power computing and security applications with RRAM devices, starting from the circuit simulations to the development of new circuital solutions.

Specifically, in Chapter 2 we present the UniMORE RRAM physics-based compact model. This model is implemented in Verilog-A, following the programming best practices, and includes the effect of RRAM devices nonidealities (i.e., self-heating, C2C, D2D, and RTN), making it an optimal solution for accurate circuit reliability simulations. A simple automated parameter extraction procedure is presented and verified on experimental data of four RRAM technologies, thus enabling the use of device-circuit co-optimization strategies.

In Chapter 3, we use the UniMORE RRAM physics-based compact model to i) assess the main reliability issues affecting conventional IMPLY-based LiM architectures, ii) to propose the novel smart-IMPLY (SIMPLY) LiM architecture, demonstrating its improved reliability and benchmarking its performance on different tasks, iii) to identify and evaluate performance and reliability trade-offs in a LBPNN implementation and proposing appropriate design strategies, and iv) to devise a novel in-memory computing architecture enabling the coexistence on the same memory array of the SIMPLY and the analog vector-matrix multiplications (VMM).

In Chapter 4, we present the result of the analysis of RTN-based TRNG circuits, i) showing the impact of different MIM stack of materials and fabrications techniques on the quality of the generated RTN considering its application as an entropy source and ii) proposing a solution for increasing the throughput of the generated output bitstream.

Finally, a general discussion of the results presented in this thesis together with an overview of possible future research directions is presented in the "Conclusions" section.

# Chapter 2

# RRAM physics-based compact modeling

# 2.1 RRAM compact models features and requirements

The study of RRAM-based circuits and architectures requires fast and accurate compact models, that can run on common SPICE or SPECTRE circuit simulators. Also, to enable the study of the reliability and performance of common RRAM-based circuits and applications compact models should reproduce both the device behavior in different operating conditions, and the effect of device nonidealities such as self-heating, variability, and RTN [75]. For instance, when studying memory array applications the effect of variability influence the number of bits that can be reliably stored in a single device while RTN reduces the read margin and thus increases the BER. In the last decades, several RRAM compact models have been proposed in the literature [97], each characterized by different strengths and weaknesses, but

none of them incorporate all the desired features, as shown in Table 2.1. In general, to be used in circuit simulators, compact models should be implemented either in SPICE or in Verilog-A, with the latter being the standard programming language for compact modeling in the semiconductor industry due to its high flexibility [98]. Indeed, most RRAM models are implemented either in SPICE or in Verilog-A, but other features are also important.

Specifically, general-purpose memristor models [99]–[102] can reproduce the median device characteristic under specific operating conditions (e.g., commonly the device IV characteristic) through simple equations. However, their accuracy is questionable when used to reproduce other operating conditions with the same set of parameters, potentially leading to errors in the circuit design. Moreover, thermal effects are not commonly included in general-purpose models, suggesting that different parameter calibrations could be required to reproduce the device behavior at different operating temperatures. Also, since the models parameters are not directly linked to the device physics, the parameter extraction procedure is non-trivial. Nevertheless, parameters extraction procedures have been developed for the Yakopcic [103] and Messaris [104] general-purpose compact models. However, the former focuses only on calibrating the device IV characteristic, thus providing limited usefulness in simulation where RRAM devices are programmed. Also, the parameter extraction procedure proposed for Messaris general-purpose compact model focuses specifically on neuromorphic computing applications, calibrating the model on the pulsed response. Despite these limitations, if appropriately used general-purpose models, thanks to their simplified modeling approach, are still a valuable tool for performing large-scale simulations without focusing on circuit reliability.

On the other hand, RRAM physics-based compact models include direct

Table 2.1: Comparison between RRAM compact models

| Story Story Of the State of the | South to Tasking | Associated by the state of the | Onesis Serie Devilies | Spirit Co.   | NO.          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|--------------|

| Yakopcic [99], [103]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>√</b>         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Not Considered        |              |              |

| TEAM/VTEAM [100], [101]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\checkmark$     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Not Considered        |              |              |

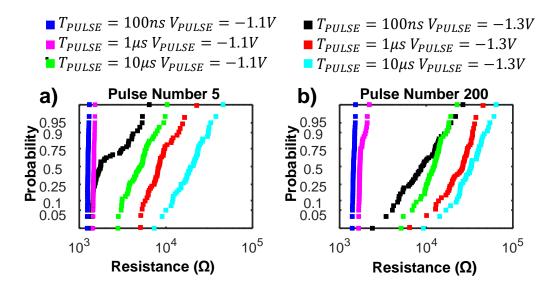

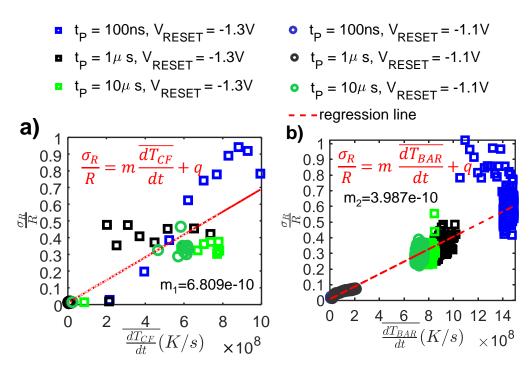

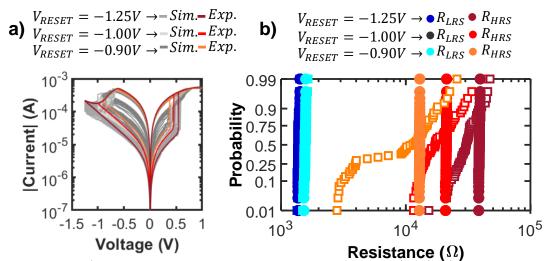

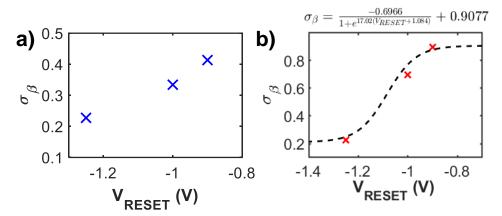

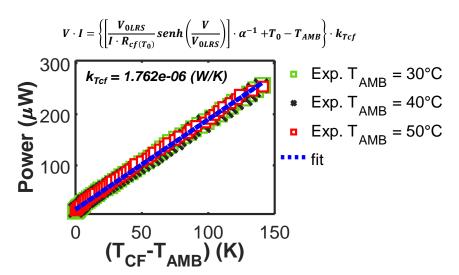

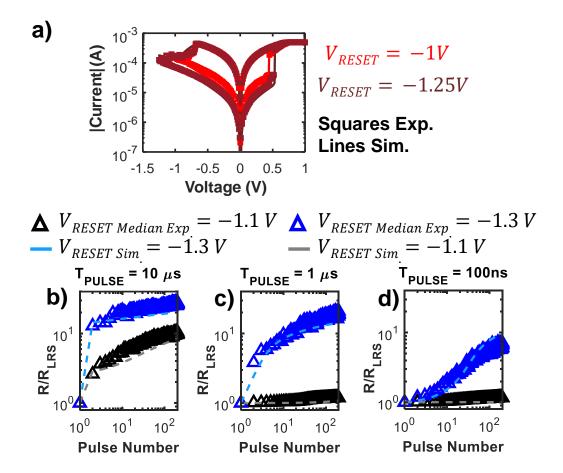

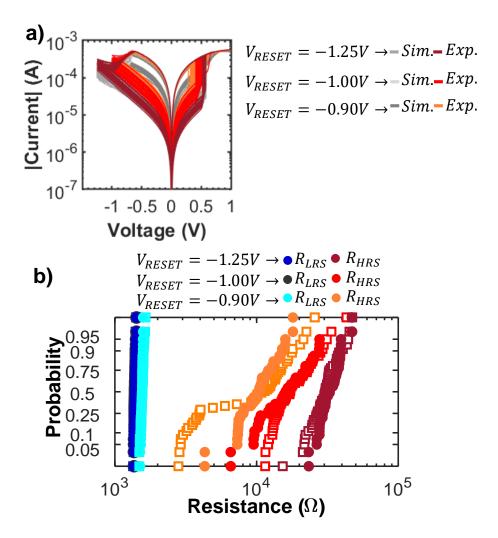

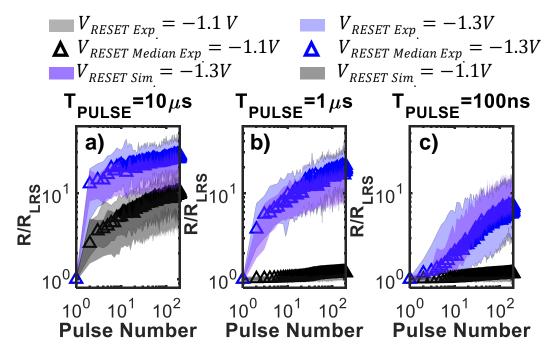

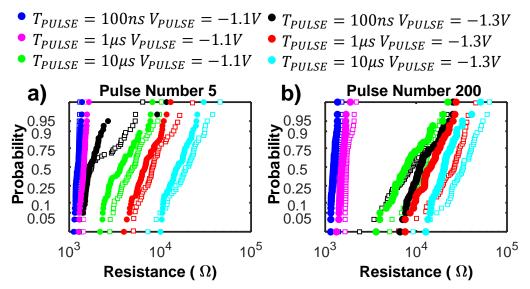

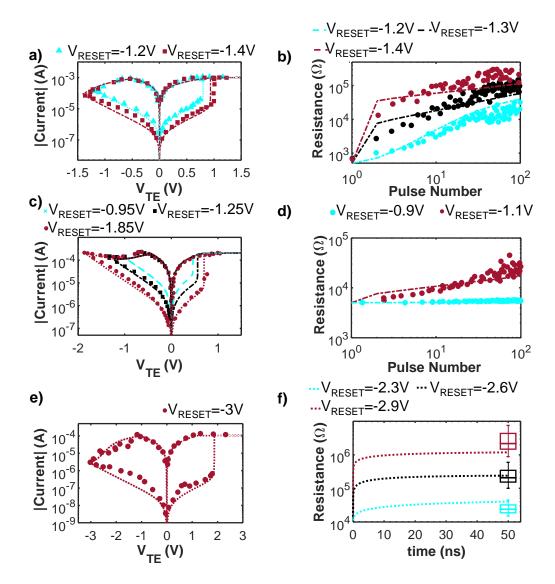

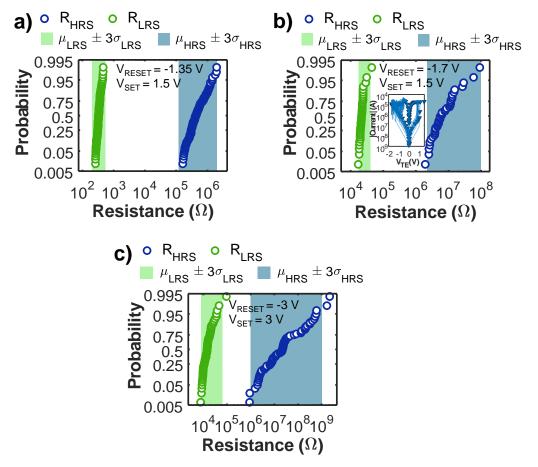

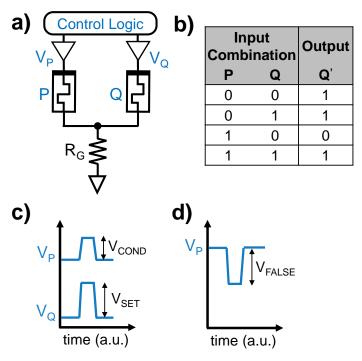

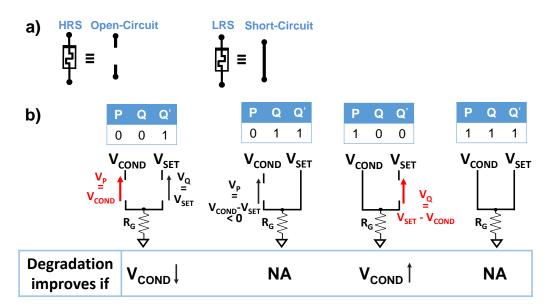

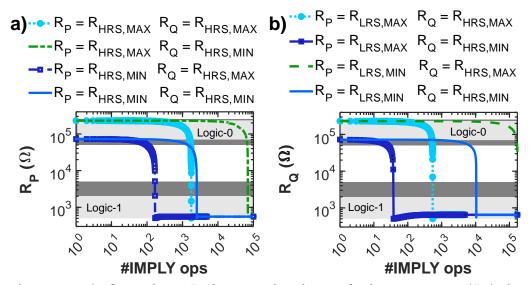

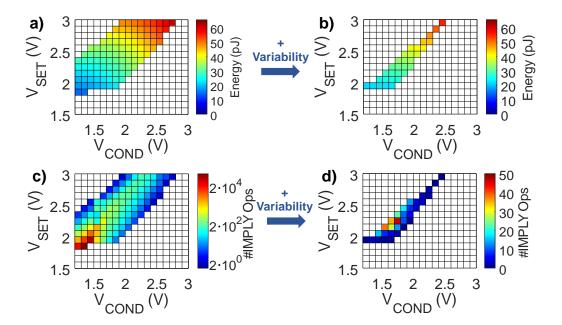

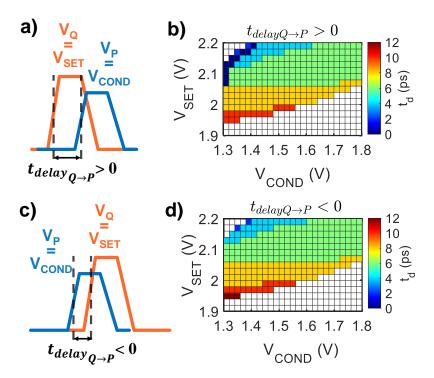

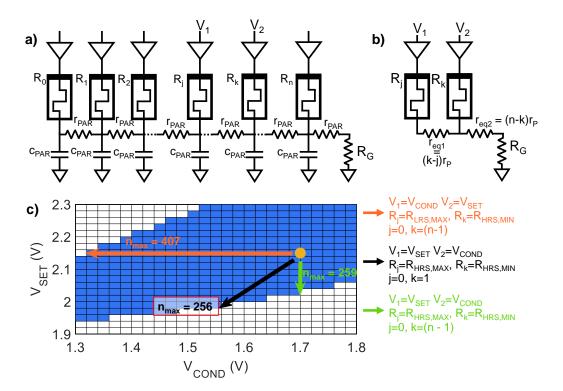

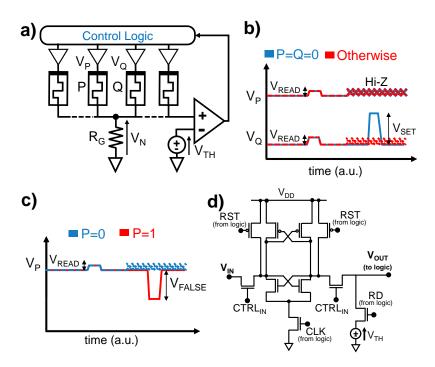

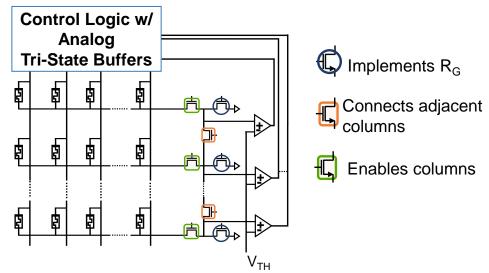

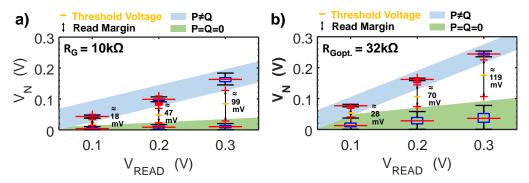

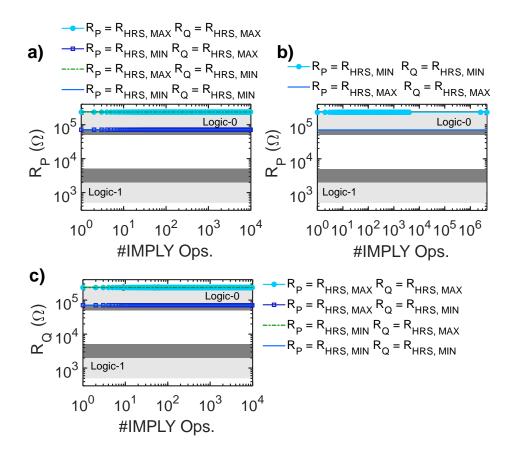

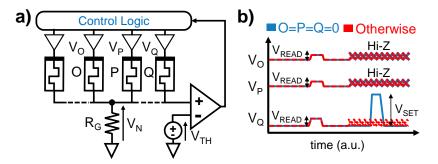

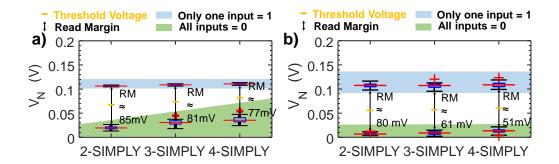

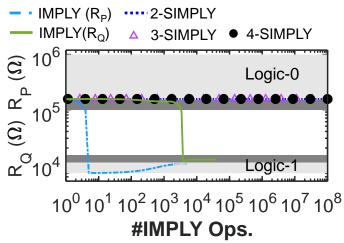

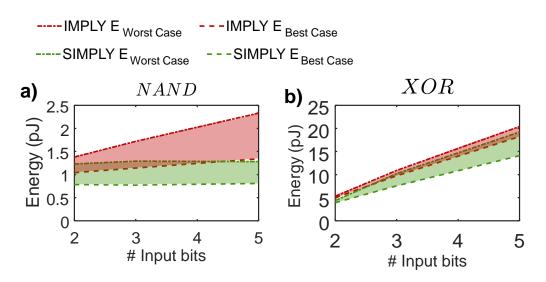

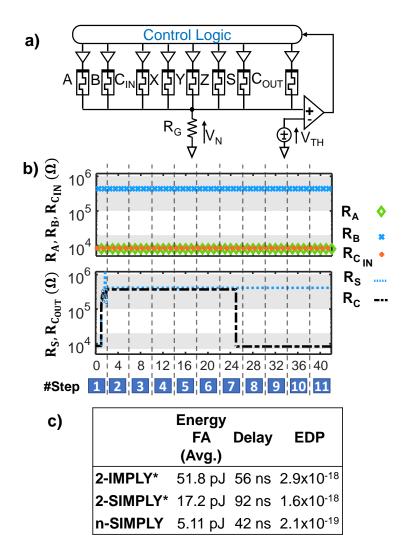

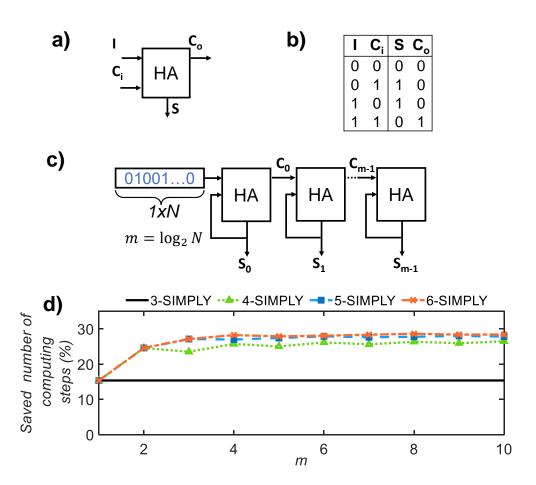

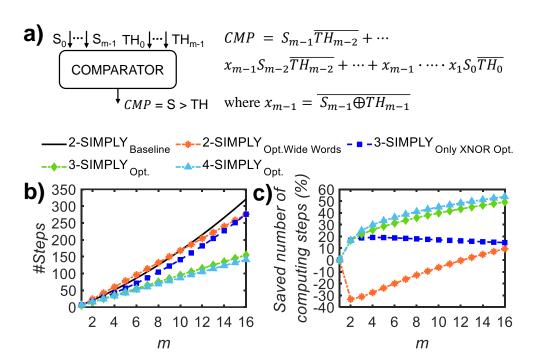

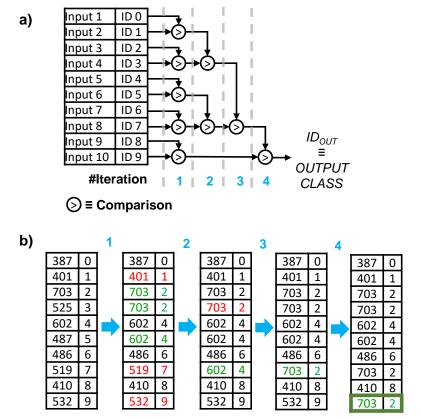

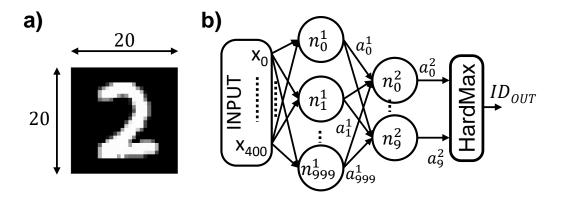

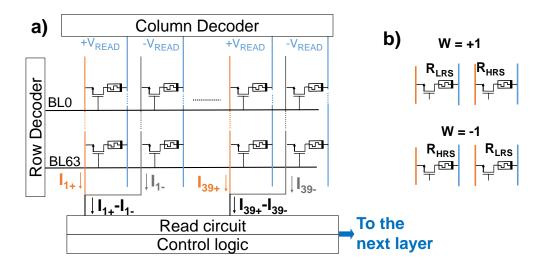

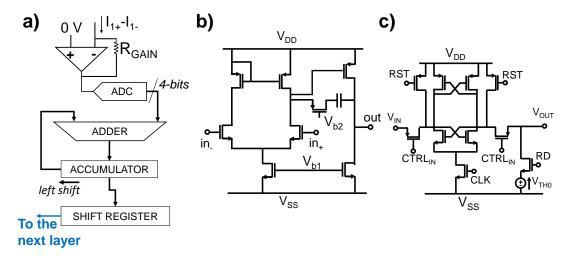

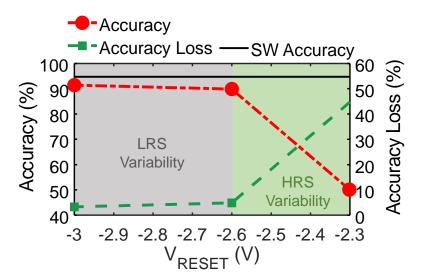

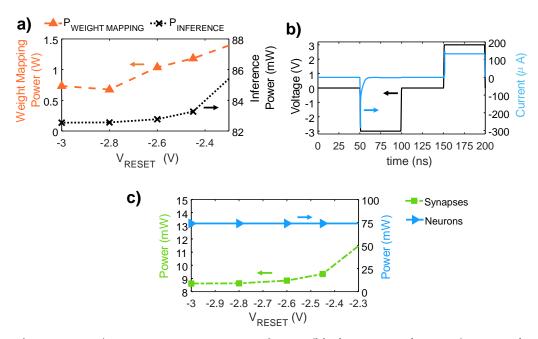

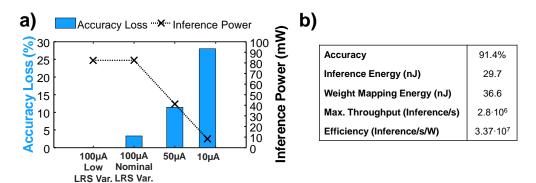

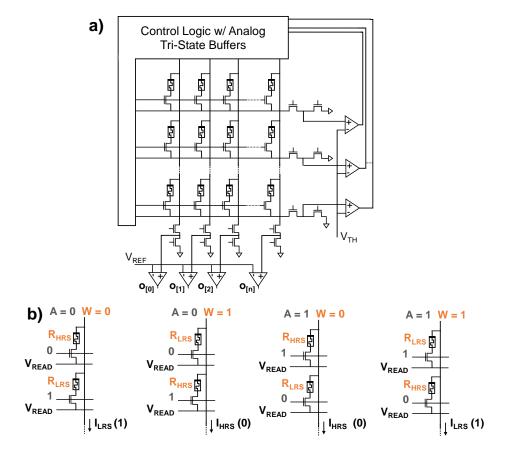

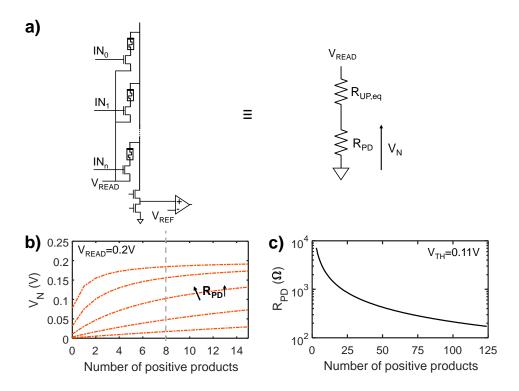

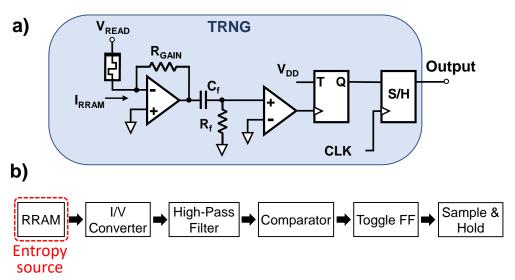

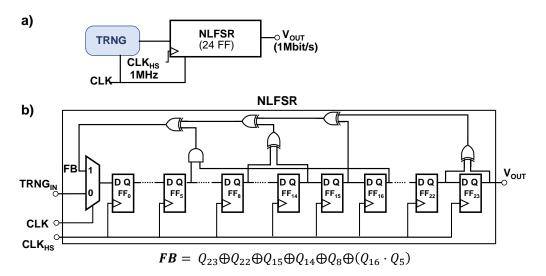

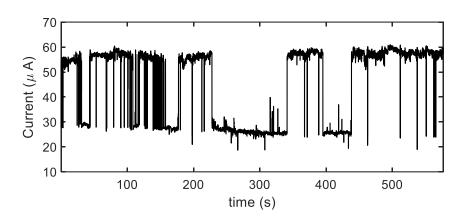

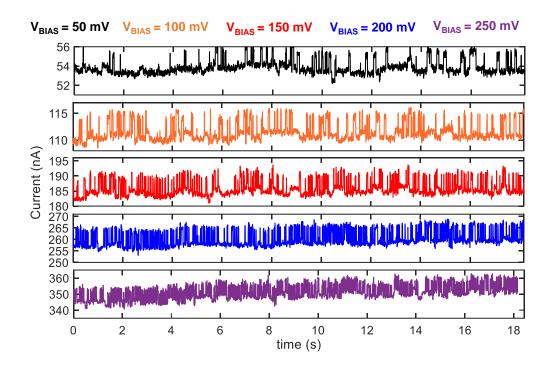

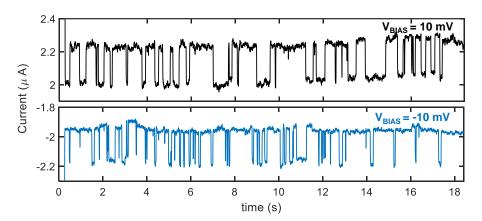

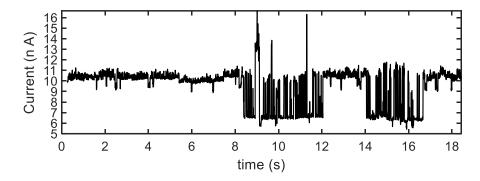

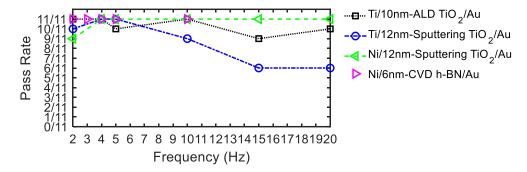

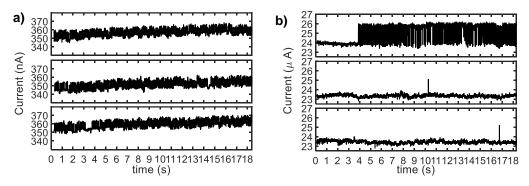

| Messaris [102], [104]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $\checkmark$     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Not Considered        |              |              |